目录

描述

输入描述:

输出描述:

参考代码

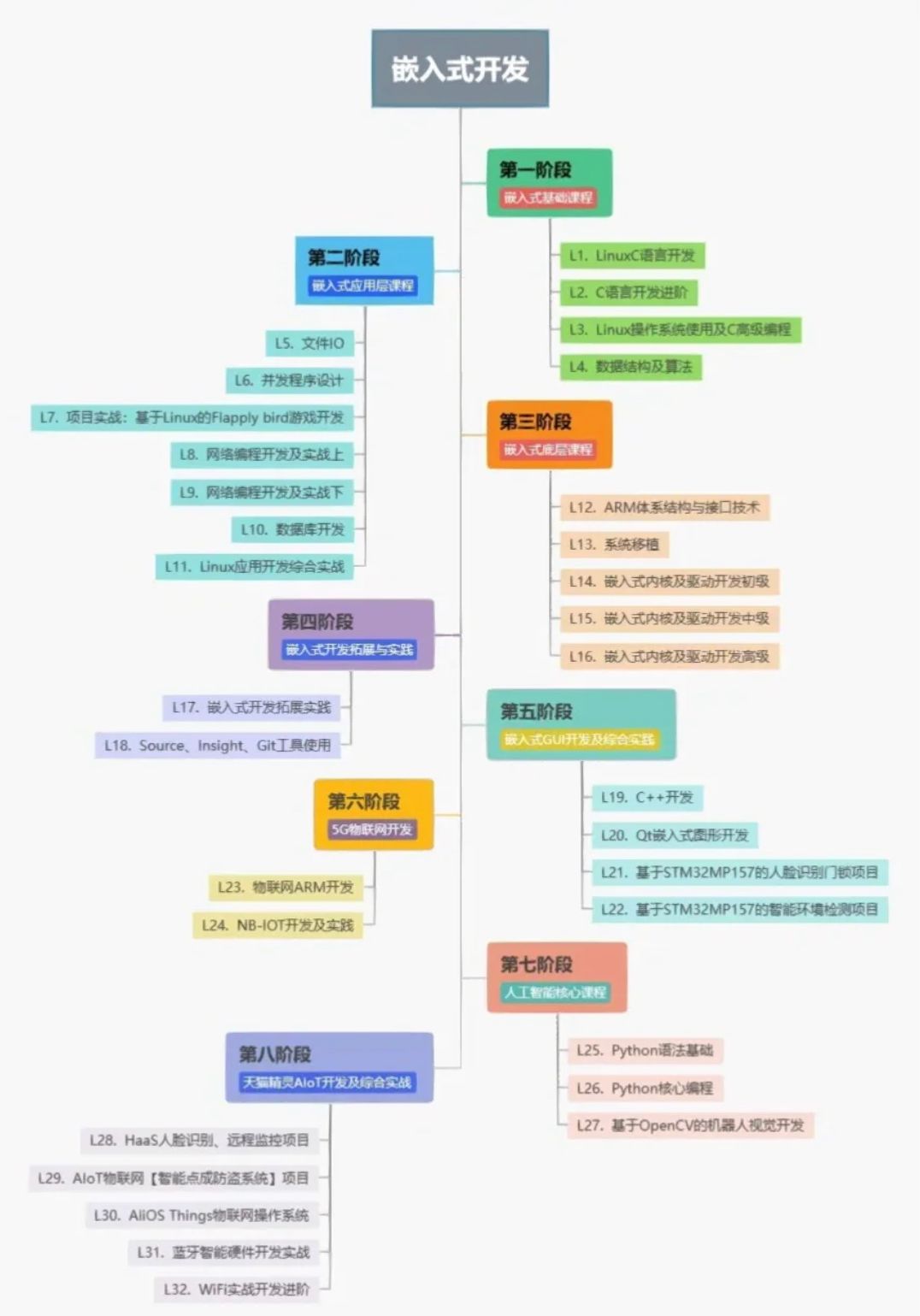

描述

题目描述:

设计一个单端口RAM,它有: 写接口,读接口,地址接口,时钟接口和复位;存储宽度是4位,深度128。

注意rst为低电平复位

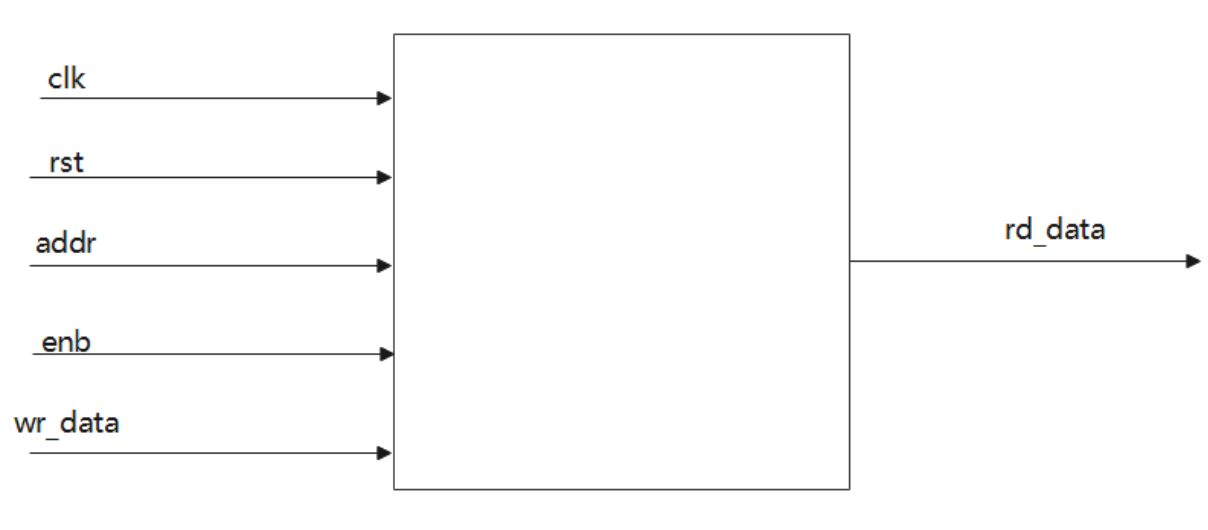

信号示意图:

输入描述:

输入信号 enb, clk, rst addr w_data

类型 wire

在testbench中,clk为周期5ns的时钟,rst为低电平复位

输出描述:

输出信号 r_data

类型 wire

参考代码

`timescale 1ns/1ns

module RAM_1port(

input clk,

input rst,

input enb,

input [6:0]addr,

input [3:0]w_data,

output wire [3:0]r_data

);

reg [6:0]mem[127:0];

integer i;

always @(posedge clk or negedge rst) begin

if(!rst) begin

for (i=0; i<127 ; i=i+1) begin

mem[i] <= 'b0;

end

end

else if (enb) begin

mem[addr] <= w_data;

end

end

assign r_data = (!enb)?mem[addr]:'b0;

endmodule