请阅读【ARM GICv3/v4 实战学习 】

文章目录

-

- GIC SGI 和 PPI 中断的使能配置

-

- GICR_ISENABLER0 操作

- 使用举例

- Summary

GIC SGI 和 PPI 中断的使能配置

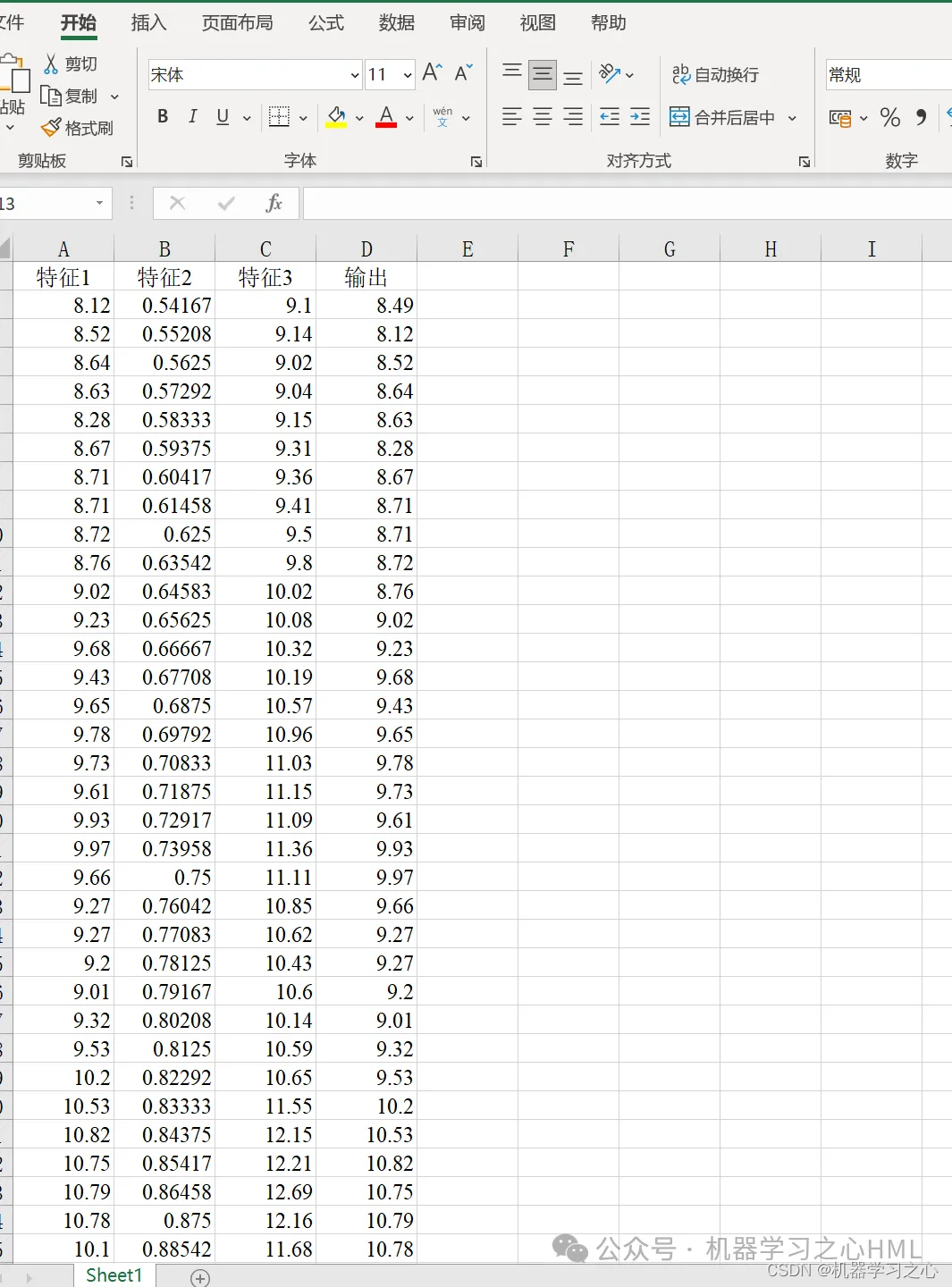

GICR_ISENABLER0寄存器(中断设置-使能寄存器0)用于启用相应的SGI(软件生成中断)或PPI(专用外设中断)向CPU接口的转发。每个重分配器(Redistributor)都提供了此寄存器的一个副本。

SET_ENABLE_BIT<X>, bit [x], for x = 31 to 0:

对于PPI和SGI,控制中断编号x向CPU接口的转发。读取和写入此位有以下行为:

0b0:如果读取,表示相应中断的转发被禁用。如果写入,没有任何效果。0b1:如果读取,表示相应中断的转发被启用。如果写入,启用相应中断的转发。写入此位为1后,随后读取此位将返回1。

GICR_ISENABLER0 操作

当一个中断的安全状态下的亲和性路由未被启用时

![[C++]入门基础(1)](https://i-blog.csdnimg.cn/direct/bfd3acf0ac0c4157a5507b4fec67112e.png)