时钟系统框图(时钟树)解析

文章目录

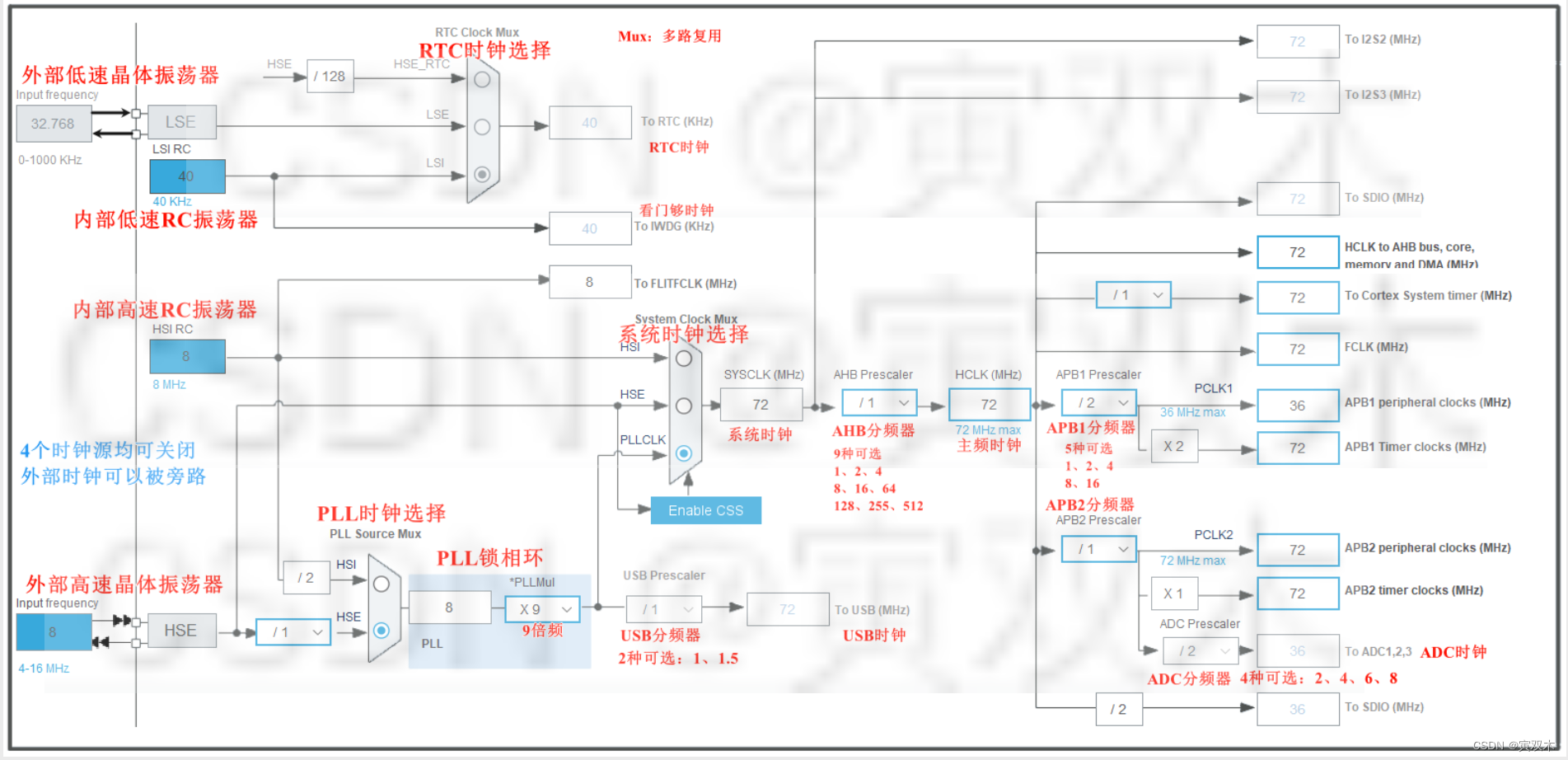

以意法半导体公司的STM32cubeIDE的stm32F103时钟树为例

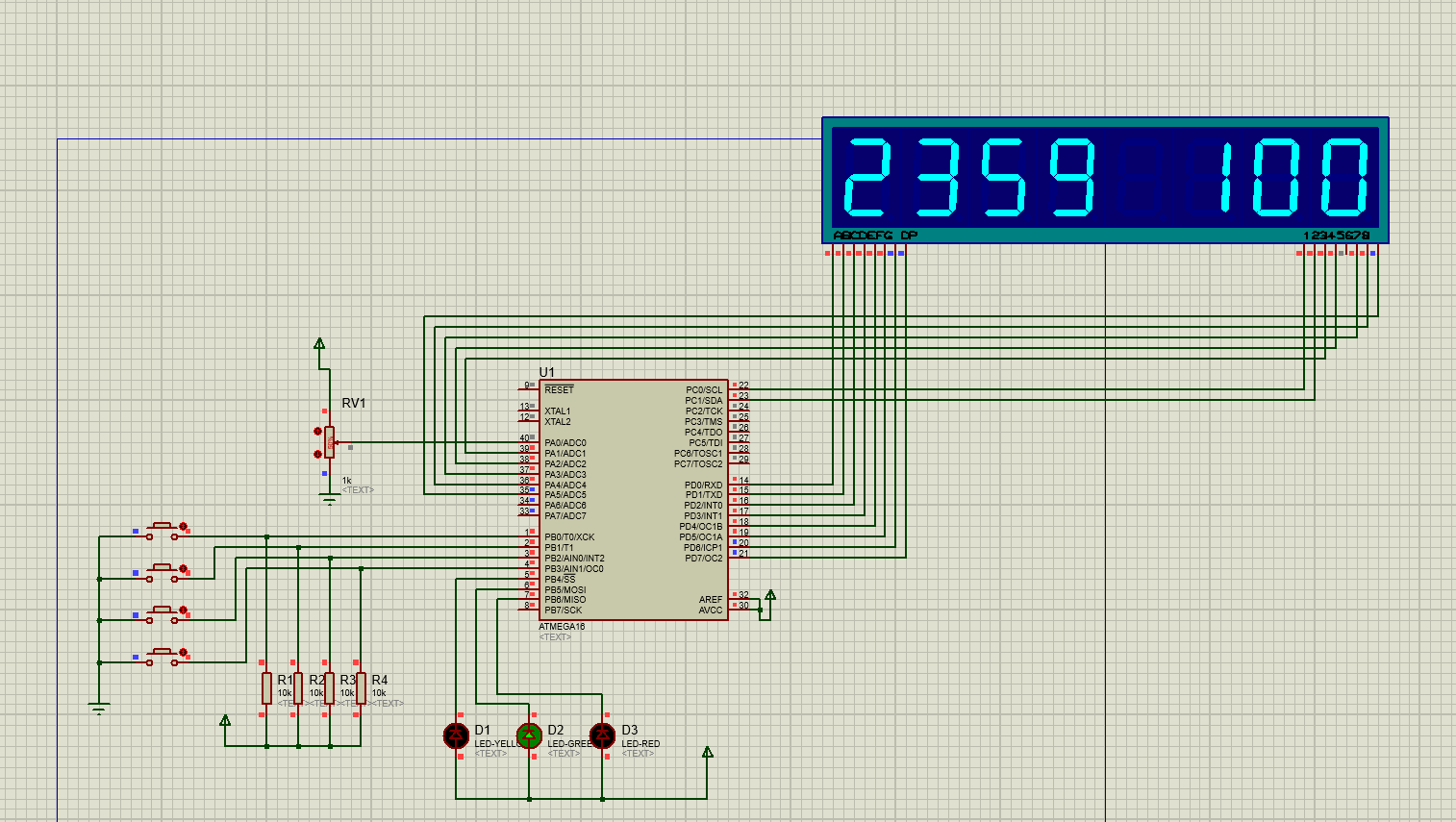

1、时钟树

2、 4个时钟源:$HSI、HSE、LSI、LSE$

①、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。RTC

②、LSI是低速内部时钟,RC振荡器,频率为约40kHz,提供低功耗时钟。

③、HSI是高速内部时钟,RC振荡器,频率为约8MHz,精度不高。IWDG

④、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

3、PLL锁相环倍频输出

PLL为锁相环倍频输出

由上图下方PLL锁相环前面的选择器可知,系统时钟有3个来源

(1)、

H

S

I

的

2

分频

HSI的2分频

HSI的2分频

(2)、

H

S

E

(

1

分频)

HSE(1分频)

HSE(1分频)

(3)、

H

S

E

的

2

分频

HSE的2分频

HSE的2分频

倍频参数可选择为2~16倍,但是其输出频率最大不得超过72M日

4、系统时钟的来源

由上图中间系统时间前面的选择器可知,系统时钟有三个来源

(1)、

H

S

I

HSI

HSI

(2)、

H

S

E

HSE

HSE

(3)、

H

S

E

经过锁相环得到的

P

L

L

C

L

K

HSE经过锁相环得到的PLLCLK

HSE经过锁相环得到的PLLCLK

5、Enable CSS(时钟监视系统)

一旦HSE失效,则自动切换至SYSCUK=HSI

6、几个重要的时钟

(1)、SYSCLK(系统时钟) :

(2)、AHB总线时钟

(3)、APB1总线时钟(低速): 速度最高36MHz

(4)、APB2总线时钟(高速): 速度最高72MHz

(5)、PLL时钟

7、RCC相关头文件和固件库源文件(标准库)

头文件:

s

t

m

32

f

10

x

r

c

c

.

h

头文件:stm32f10x_rcc.h

头文件:stm32f10xrcc.h

源文件:

s

t

m

32

f

10

x

r

c

c

.

c

源文件:stm32f10x_rcc.c

源文件:stm32f10xrcc.c

(1)、时钟源使能配置:

RCC_LSEConfig() 、RCC_HSEConfig()、

RCC_HSICmd() 、 RCC_LSICmd() 、 RCC_PLLCmd() ……

(2)、时钟源相关配置:

RCC_PLLConfig ()、 RCC_SYSCLKConfig() 、

RCC_RTCCLKConfig() …

(3)、分频器系数选择配置:

RCC_HCLKConfig() 、 RCC_PCLK1Config() 、 RCC_PCLK2Config()…

(4)、外设时钟使能:

RCC_APB1PeriphClockCmd(): //APB1线上外设时钟使能

RCC_APB2PeriphClockCmd(); //APB2线上外设时钟使能

RCC_AHBPeriphClockCmd(); //AHB线上外设时钟使能

(5)、 其他外设时钟配置:

RCC_ADCCLKConfig (); RCC_RTCCLKConfig();

(6)、状态参数获取参数:

RCC_GetClocksFreq();

RCC_GetSYSCLKSource();

RCC_GetFlagStatus()

(7)、RCC中断相关函数 :

RCC_ITConfig() 、 RCC_GetITStatus() 、 RCC_ClearITPendingBit()…

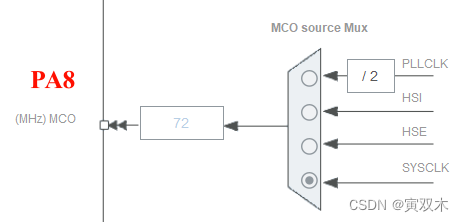

8、时钟的输出口

stm32F103的PA8是时钟输出端口MCO,有4个时钟来源

(1)、

P

L

L

C

L

K

的

2

分频

PLLCLK的2分频

PLLCLK的2分频

(2)、

H

S

I

HSI

HSI

(3)、

H

S

E

HSE

HSE

(4)、

S

Y

S

C

L

K

SYSCLK

SYSCLK

┈┈┈┈▕▔╲┈┈┈┈┈┈┈ ┈┈┈┈▕▔╲┈┈┈┈┈┈┈ ┈┈┈┈▕▔╲┈┈┈┈┈┈┈┈

┈┈┈┈┈▏▕┈┈┈┈┈┈┈ ┈┈┈┈┈▏▕┈┈┈┈┈┈┈ ┈┈┈┈┈▏▕┈┈┈┈┈┈┈ ┈

┈┈┈┈┈▏ ▕▂▂▂▂▂┈┈┈┈┈┈┈▏ ▕▂▂▂▂▂┈┈┈┈┈┈┈▏ ▕▂▂▂▂▂┈┈┈

▂▂▂▂╱┈┈▕▂▂▂▂▏┈ ▂▂▂▂╱┈┈▕▂▂▂▂▏┈ ▂▂▂▂╱┈┈▕▂▂▂▂▏┈┈

▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈ ▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈ ▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈

▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈ ▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈ ▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈

▔▔▔▔╲▂▂▕▂▂▂▂▏┈ ▔▔▔▔╲▂▂▕▂▂▂▂▏┈ ▔▔▔▔╲▂▂▕▂▂▂▂▏┈┈