设计连接性

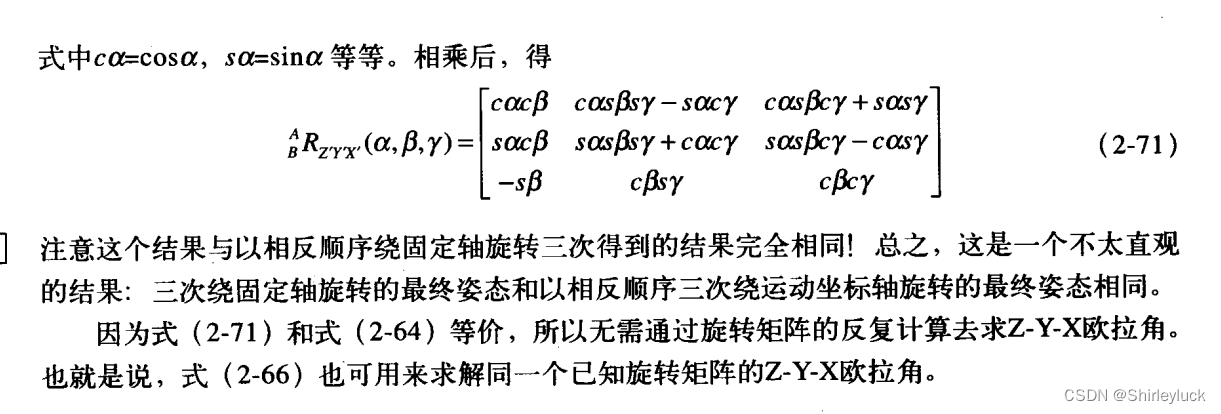

IP集成商提供设计师协助,帮助您完成连接过程

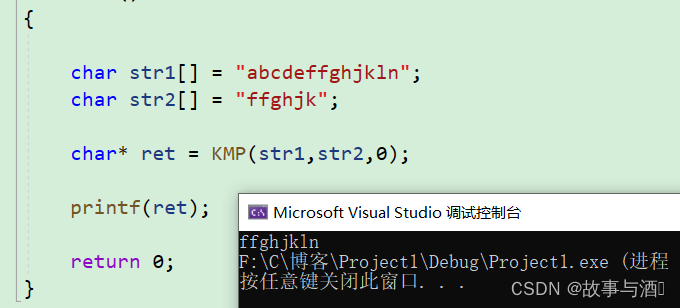

设计。图3显示了MHS的一个示例,图4显示了设计帮助

可在IP集成商中获得

地址映射

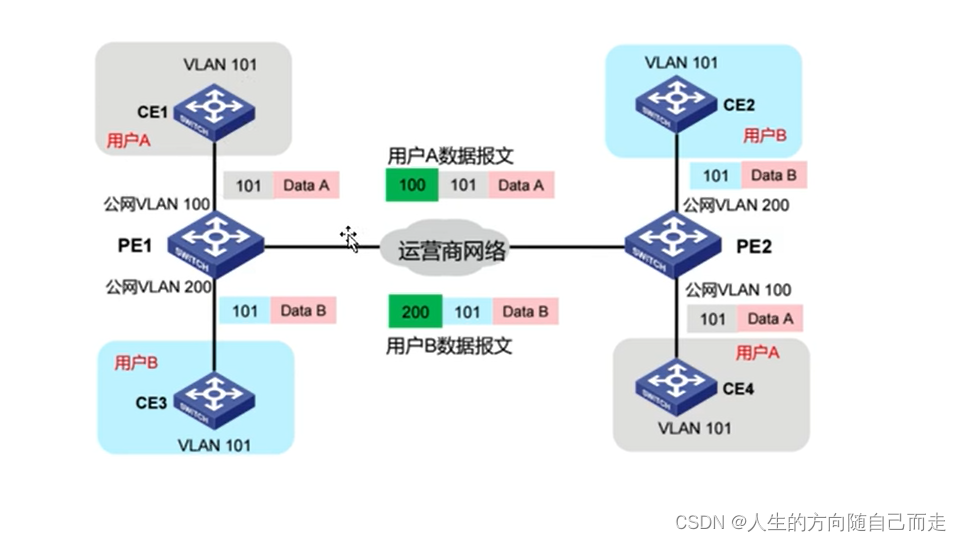

在XPS中,无论主机访问从机IP,每个从机都有相同的地址。IP

integrator为基于master的寻址提供支持。因此,同一个从属可以

两个不同的主控器所看到的两个不同地址。图5和图6说明了这一点

解决从MHS到IP集成商的变化。

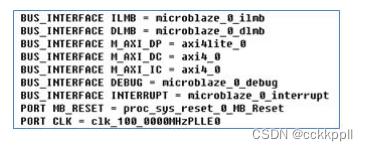

时钟和重置

XPS通过使用时钟生成器IP提供中央时钟机制。时钟

生成器识别所有IP的时钟要求,并生成所需的MMCM/PLL

配置作为IP的一部分。

在IP积分器中,使用clocking_wizard进行时钟配置。

重要!您必须输入所需频率作为时钟向导IP的一部分。的属性

生成的时钟(如频率和相位)从时钟IP传播到单个

通过使用IP实现的参数传播方法。

有关详细信息,请参阅以下文档:

•Vivado Design Suite用户指南:嵌入式处理器硬件设计(UG898)

•Vivado Design Suite用户指南:使用IP Integrator设计IP子系统(UG994)

•Vivado Design Suite用户指南:使用IP进行设计(UG896)

互连配置

LogiCORE™IP高级可扩展接口(AXI)互连核心连接一个或多个

AXI存储器映射的主设备到一个或多个存储器映射的从设备。

设置调试

您可以通过在块设计中选择一个网络,右键单击,然后标记要调试的信号

在IP集成程序中选择“标记调试”。这通过将

在生成的HDL代码中适当的网络保持属性。然后设计可以

可以在合成的网表中插入(一个或多个)合成的和调试的核。ILA也可以是

在块设计中实例化,AXI接口或单个I/O端口可以连接到

ILA稍后进行监控。

基于Zynq 7000平台处理器和基于MicroBlaze处理器的设计也支持

交叉触发功能。这本质上意味着处理器有能力触发

并由Vivado集成逻辑分析仪触发。

有关详细信息,请参阅以下文档:

•Vivado Design Suite用户指南:编程和调试(UG908)

•Vivado设计套件教程:嵌入式处理器硬件设计(UG940)

ELF文件的关联

在基于微处理器的设计中(例如MicroBlaze处理器设计或Zynq 7000设备

包含MicroBlaze处理器的设计),Vitis软件中生成的ELF文件

开发平台(或在另一个软件开发工具中)可以导入并关联

Vivado的方块设计。然后,您可以从中对比特流和ELF文件进行编程

Vivado并在目标硬件上运行它。XPS和IP积分器之间的过程相同。

请参阅Vivado Design Suite用户指南:使用IP Integrator(UG994)设计IP子系统

更多信息。