文章目录

- ModelSim 路径设置

- 创建 RAM

- 进行仿真

本文主要介绍如何在包含 IP 核的 Quartus 项目中使用 Modelsim 进行仿真,本文基于 IP 核

RAM: 2-PORT,其他 IP 核类似。

ModelSim 路径设置

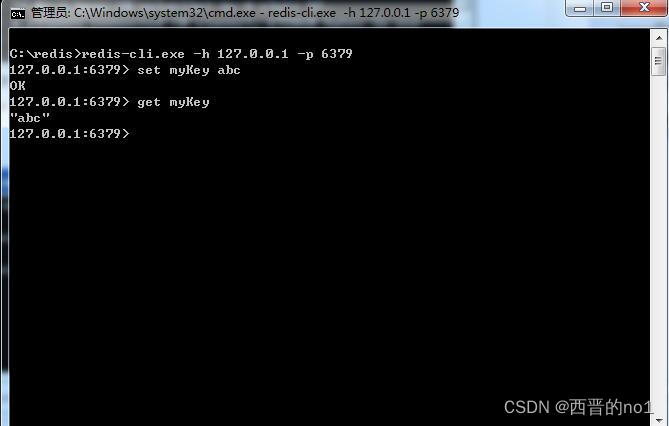

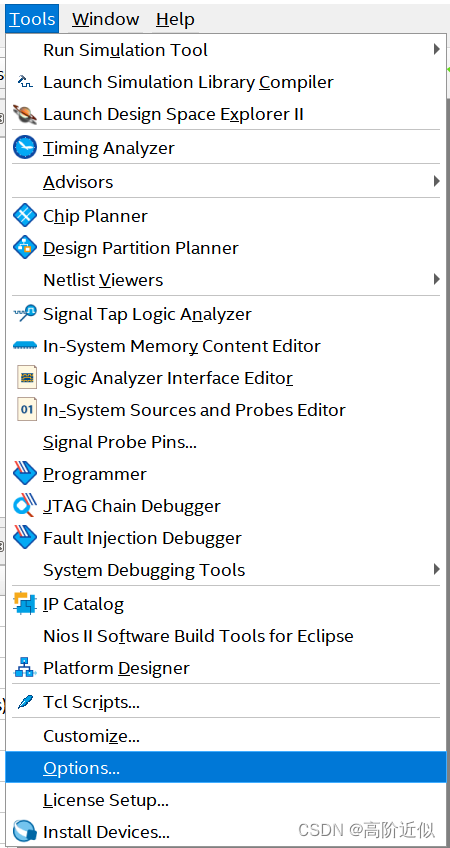

点击 Tools->Options

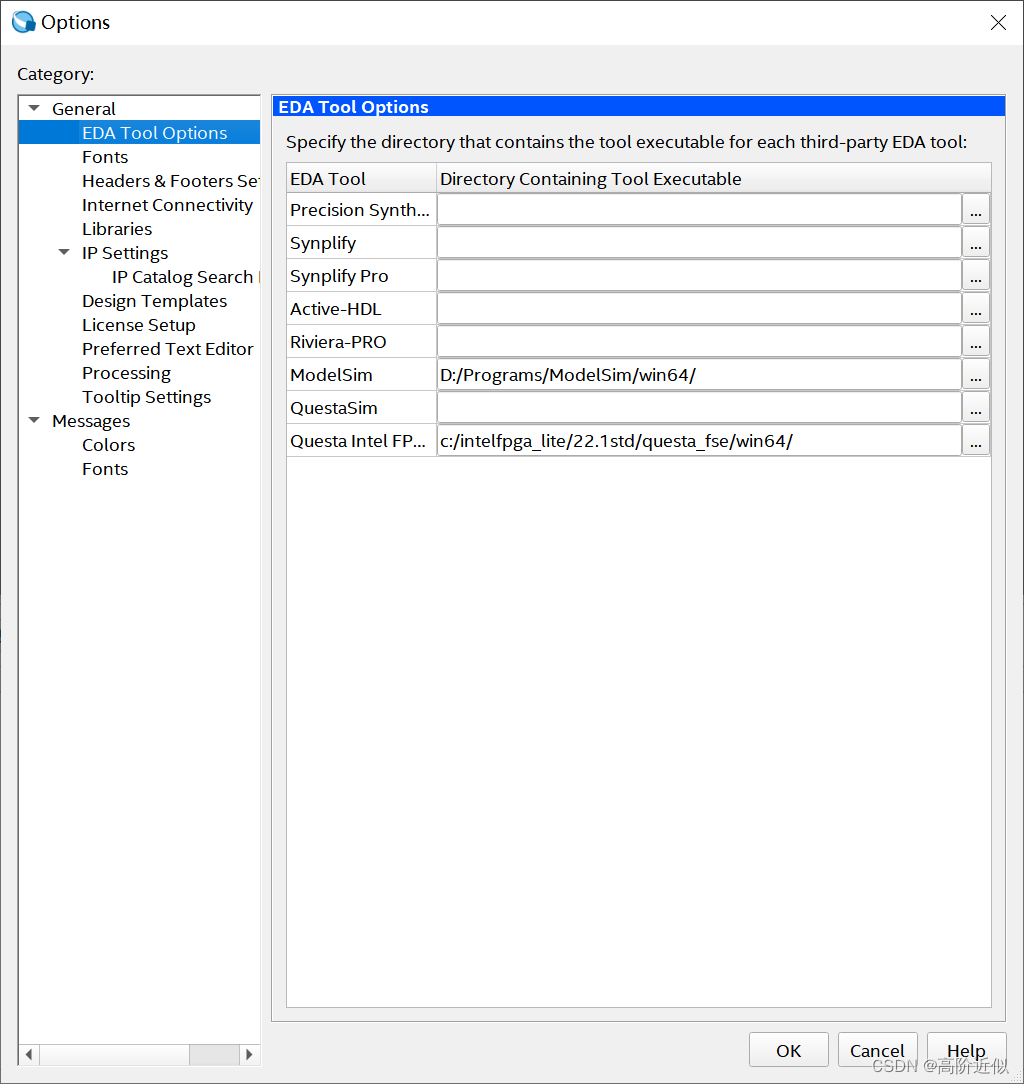

点击 EDA Tool Options,设置好 ModelSim 的路径,需要注意的是,路径一定要以 / 结尾,否则无法正确进行仿真(比如 D:/Programs/ModelSim/win64 就是错误的写法)。

如果使用

Questa Intel FPGA来仿真,也一定要检查对应的路径是否是/结尾

创建 RAM

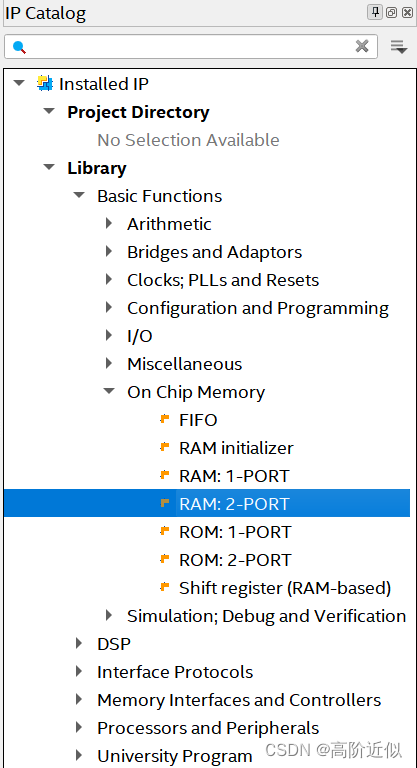

打开 IP Catalog,双击 RAM: 2-PORT

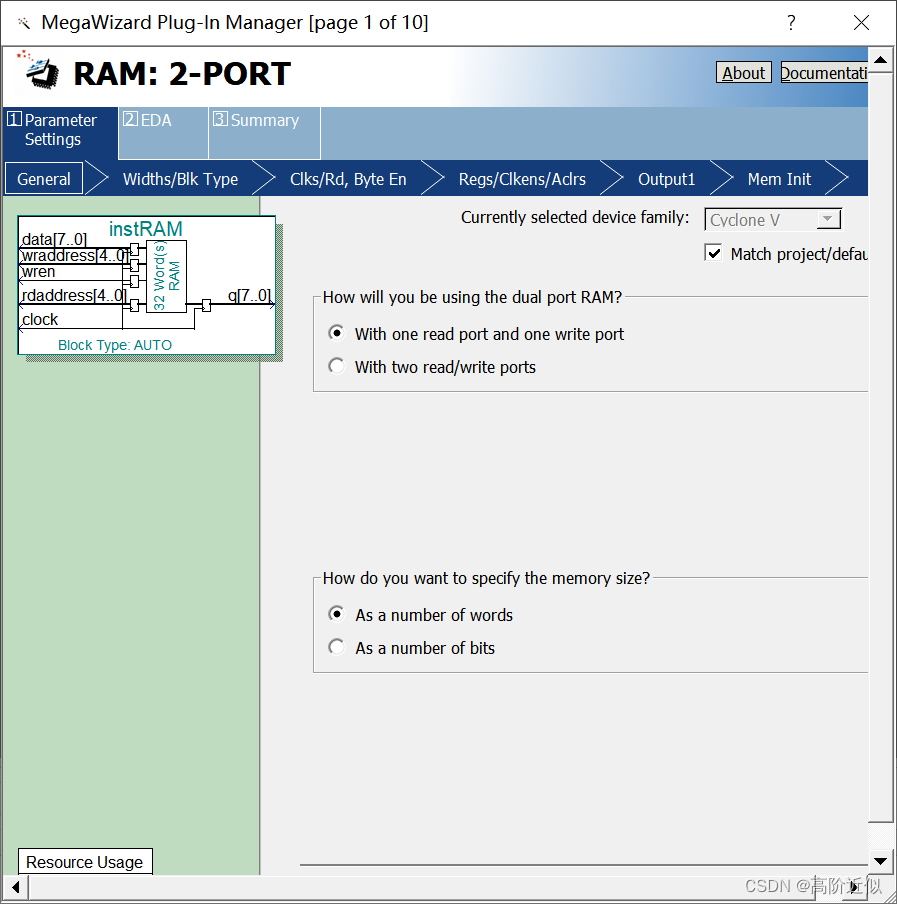

首先设置好 IP variation 的路径,接下来会进入 IP 核配置界面。

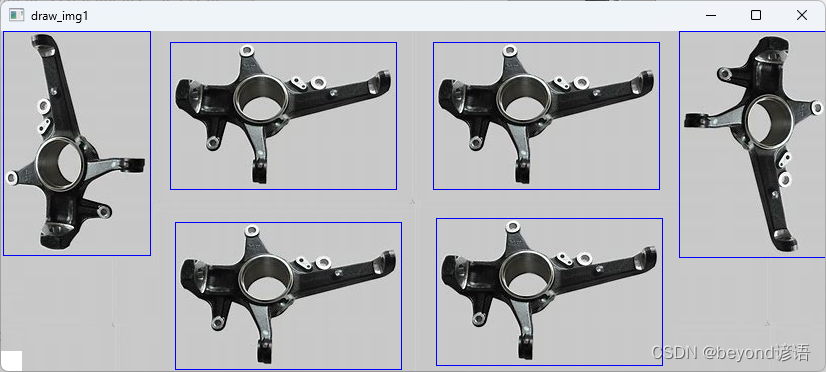

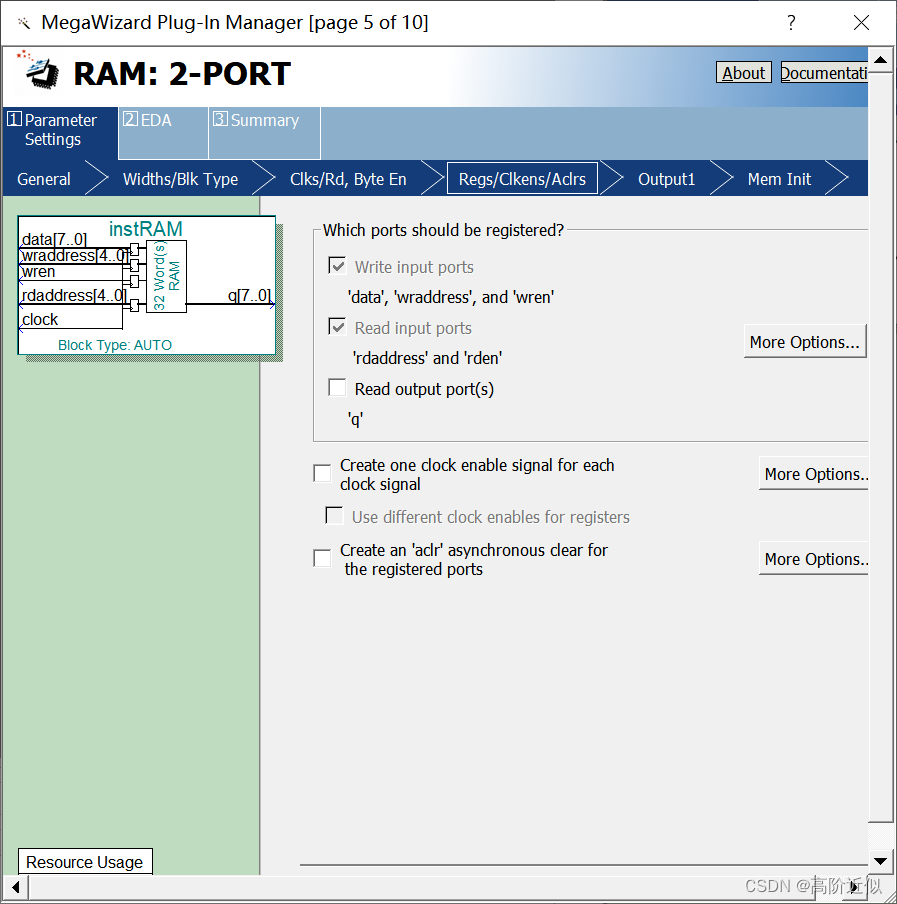

按个人需求配置 RAM 即可,有几个地方需要注意。首先下图中 Read output ports 如果勾选的话,输出结果会延迟一个周期,这里取消勾选

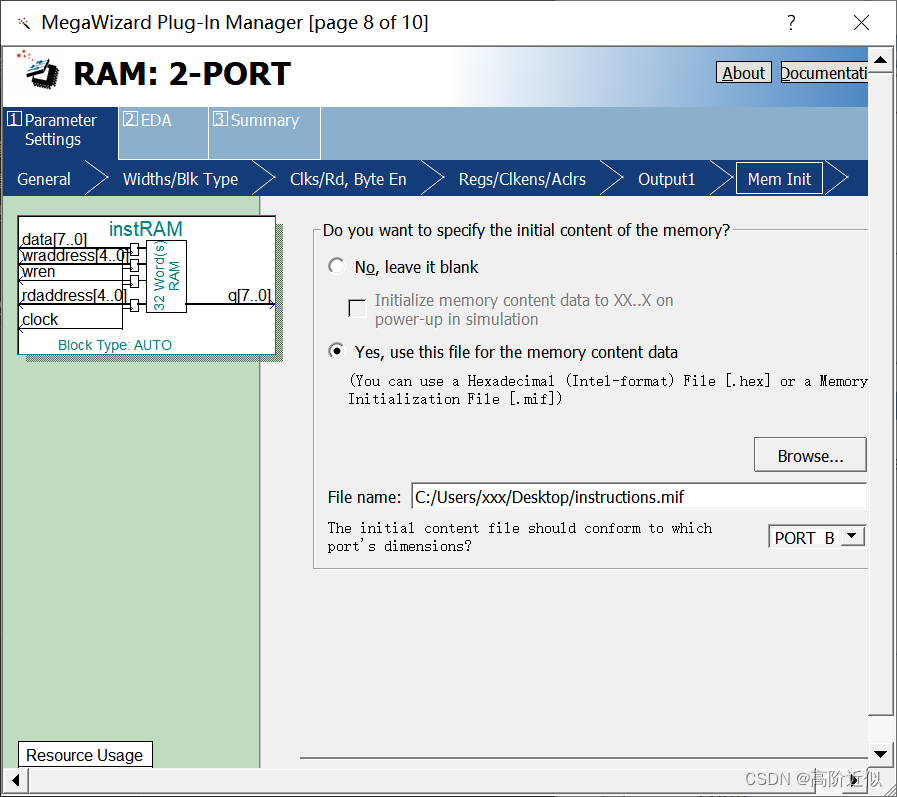

其次,可以使用 .hex 或者 .mif 文件来对 RAM 进行初始化,这两种文件如何创建后面会介绍。如果要用 Modelsim 来仿真,下图中 .hex 或者 .mif 文件的路径最好还是使用绝对路径,否则 ModelSim 可能找不到这个文件

如果要使用相对路径,那么最好将

.hex或者.mif文件保存在当前项目所在的目录下,即File name那一栏应该是./YOUR_FILENAME.mif

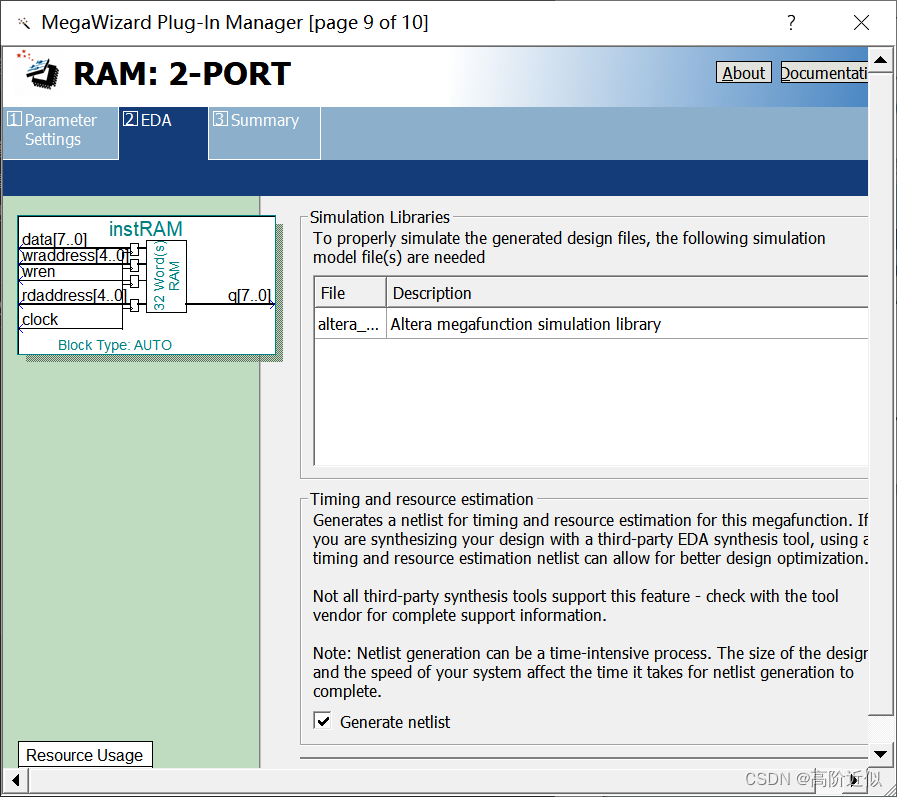

最后非常重要的是,下图中 Generate netlist 一定要勾选上,否则 ModelSim 无法仿真

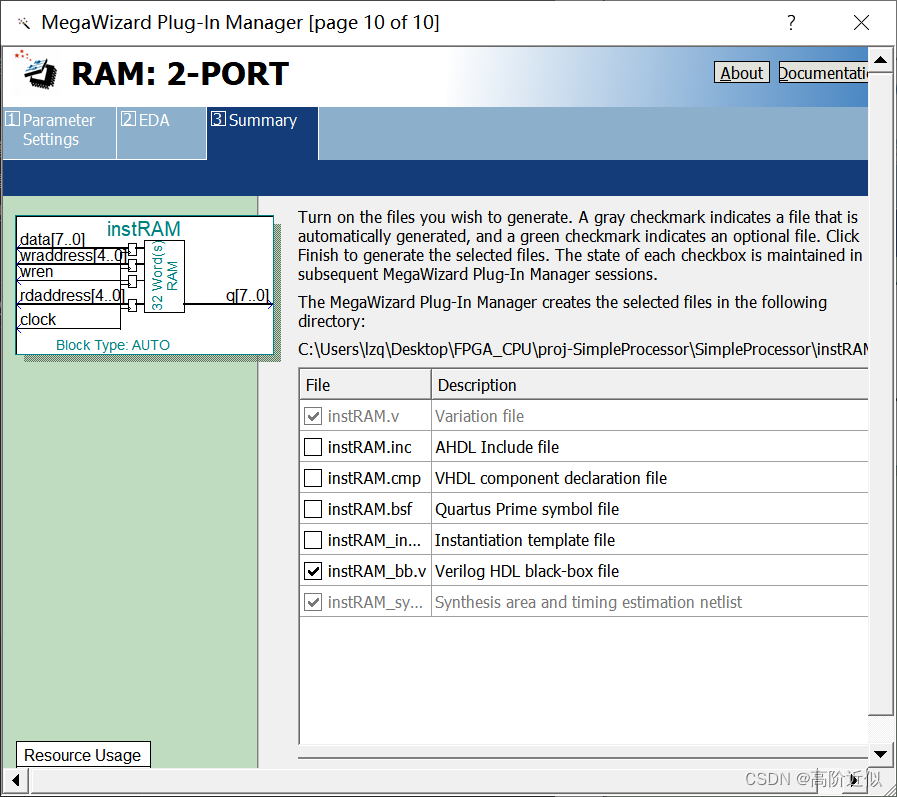

最后,点击 Finish 即可生成 IP 核

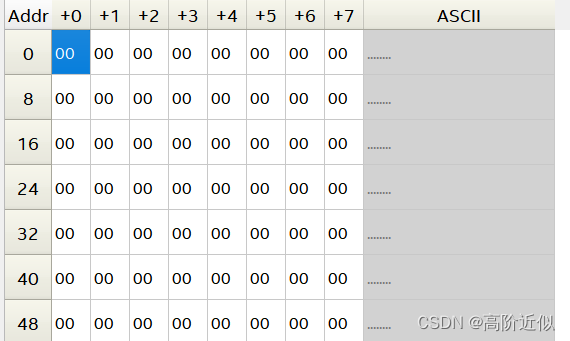

.hex或者.mif文件的生成:

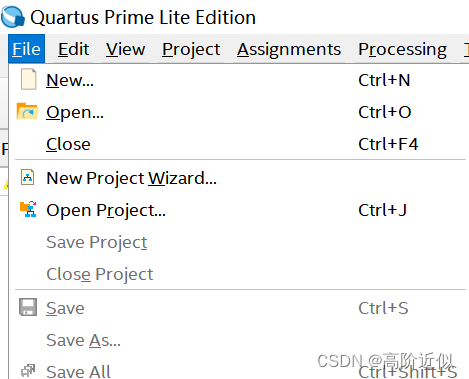

点击

File->New

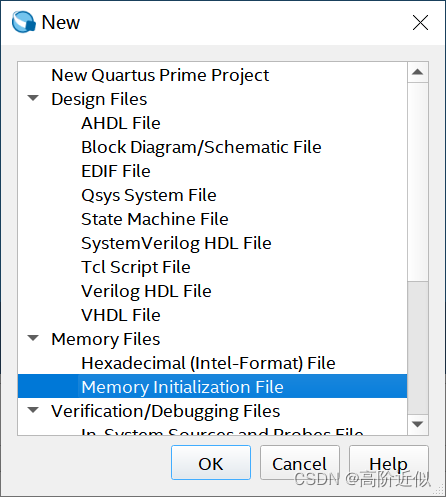

点击

Memory Files下面的Hexadecimal File或者Memory Initialization File,这里选择mif

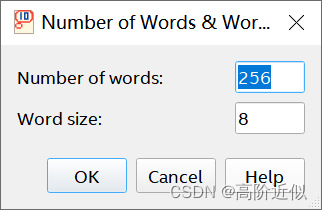

设置好 words 的数量和大小,需要和 RAM 保持一致

在下面填入对应的值后保存即可

进行仿真

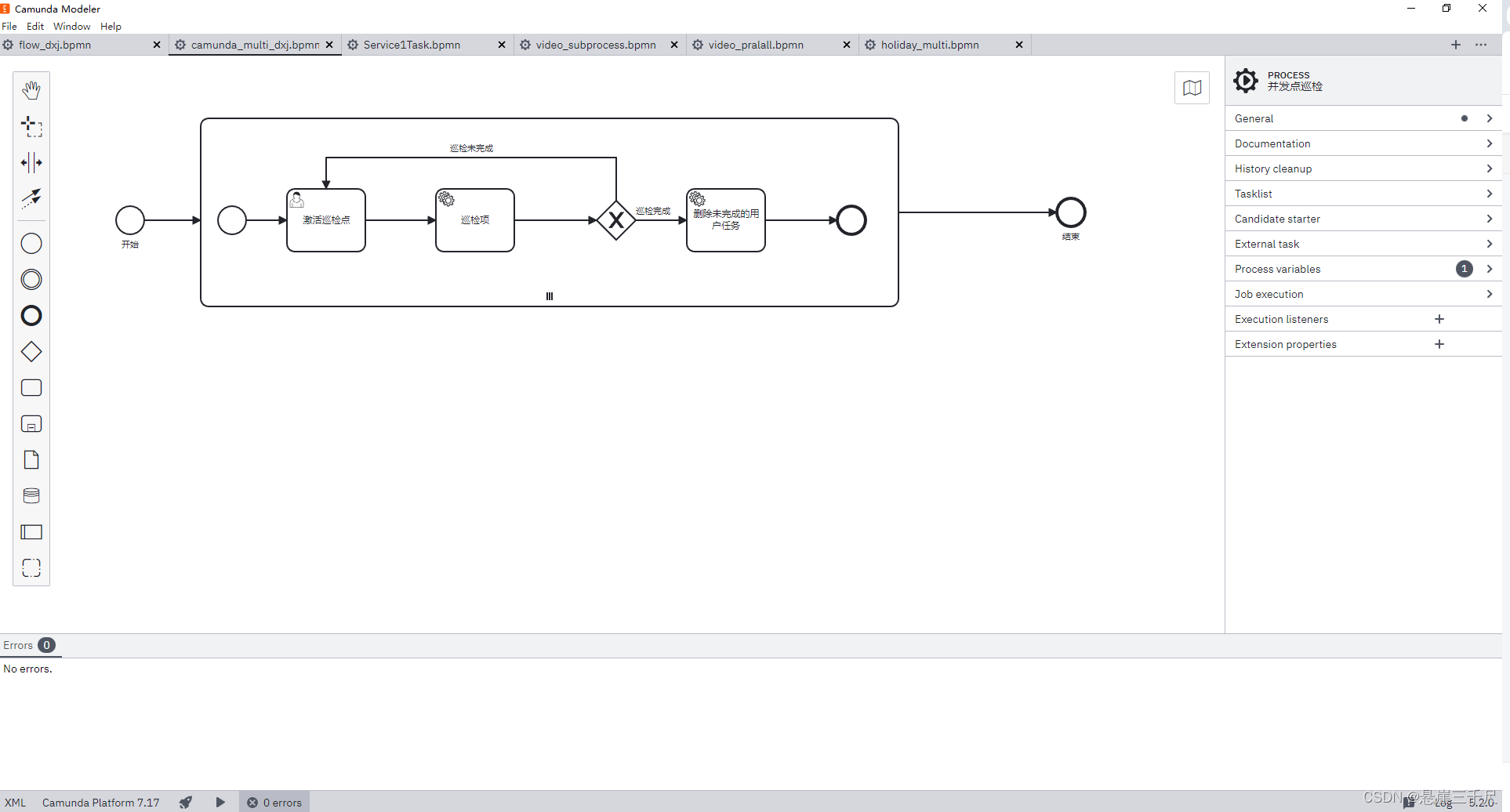

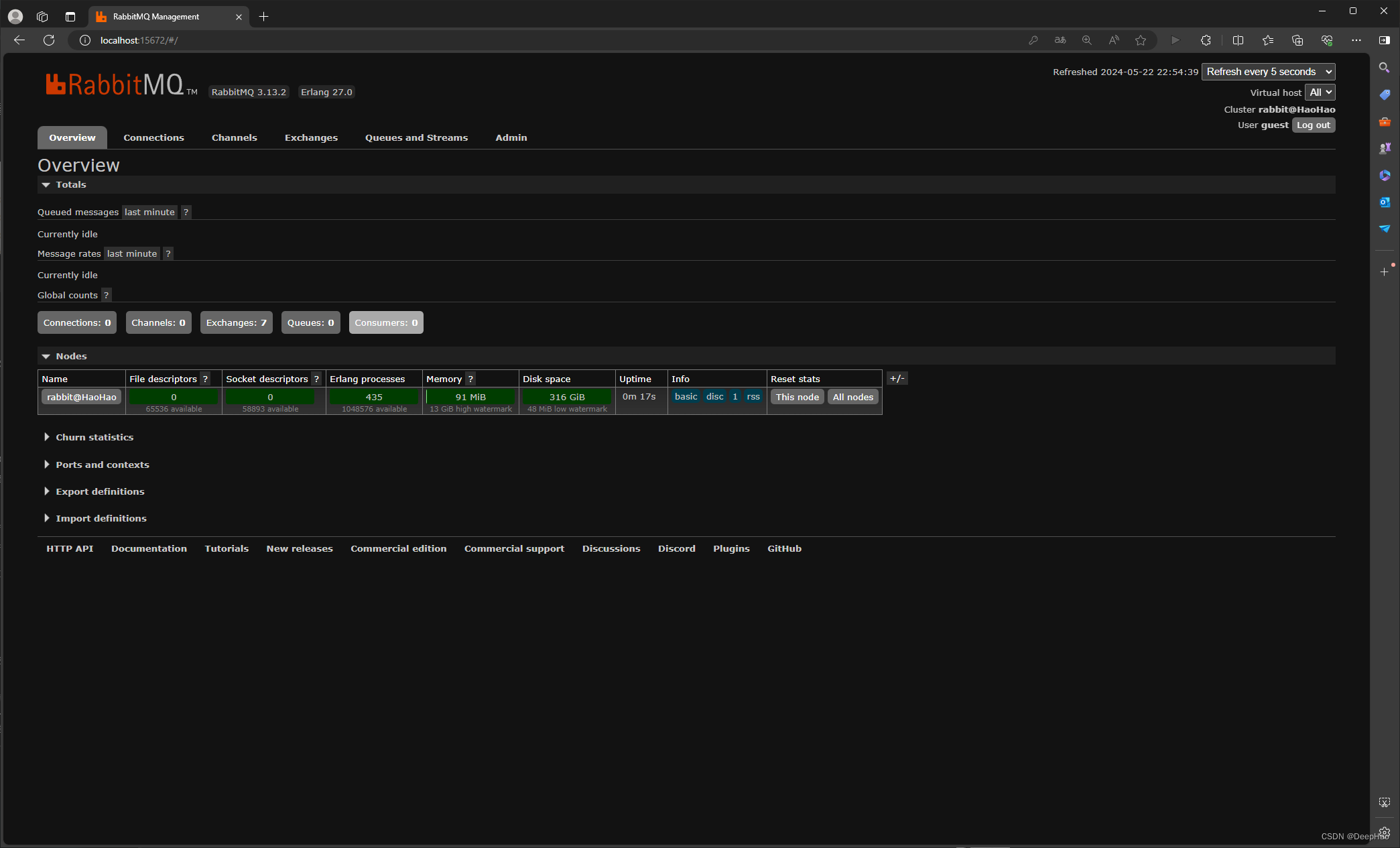

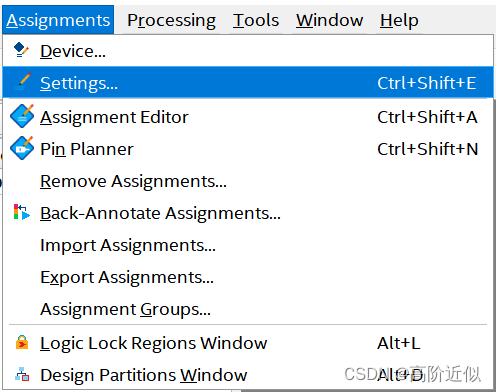

点击 Assignments->Settings

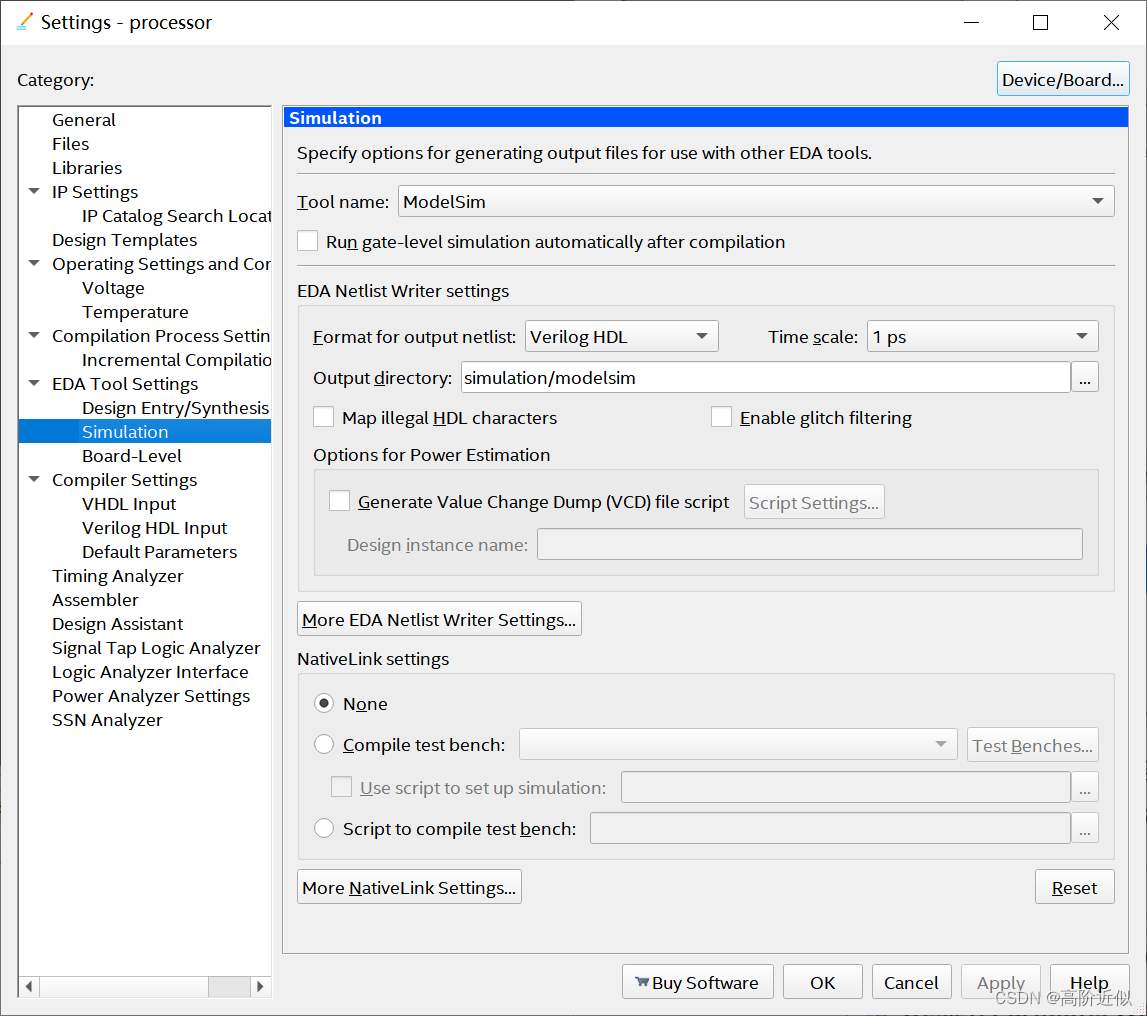

点击 EDA Tool Settings->Simulation,将 Tool name 设置为 ModelSim

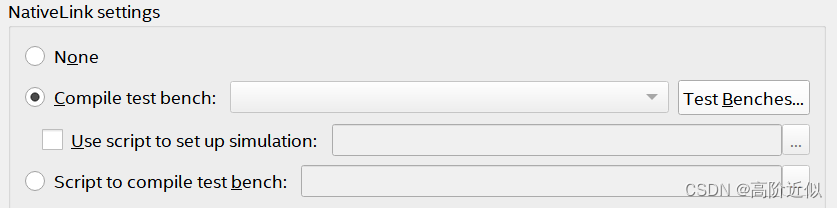

接下来指定 Test bench,点击下图中的 Test Benches

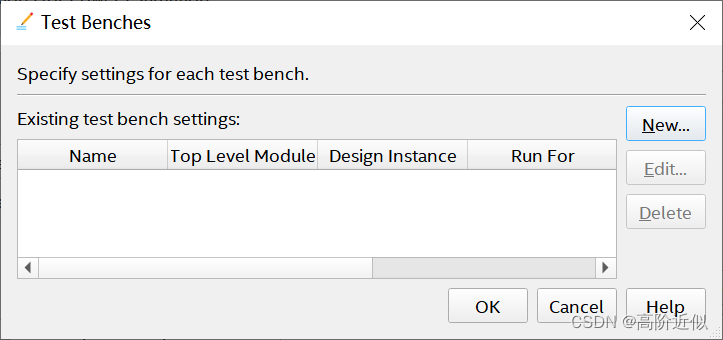

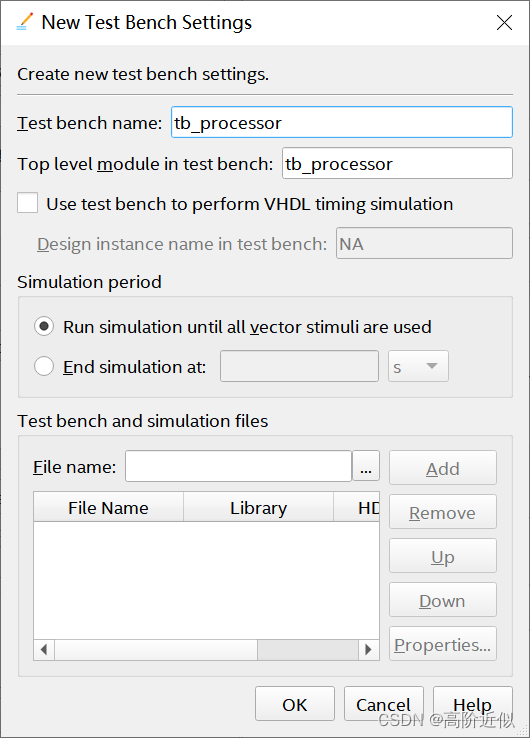

点击 New

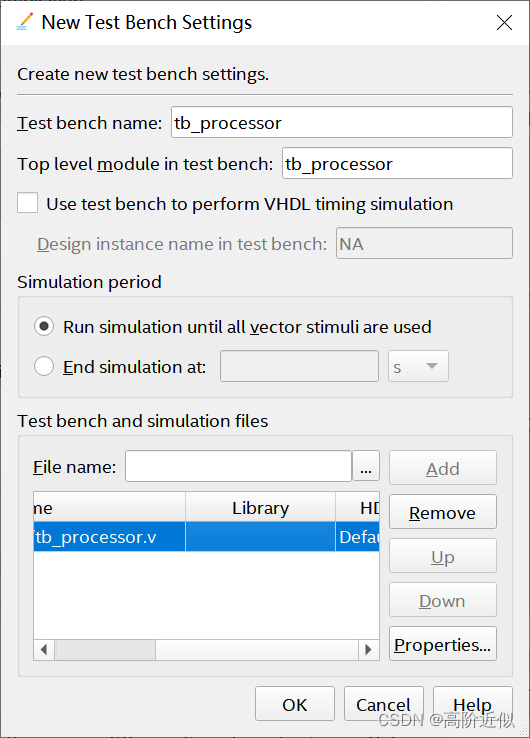

设置好名字,然后点击 File name 右边的三个点来添加 tb 文件

添加好后依次点击 OK 退出即可

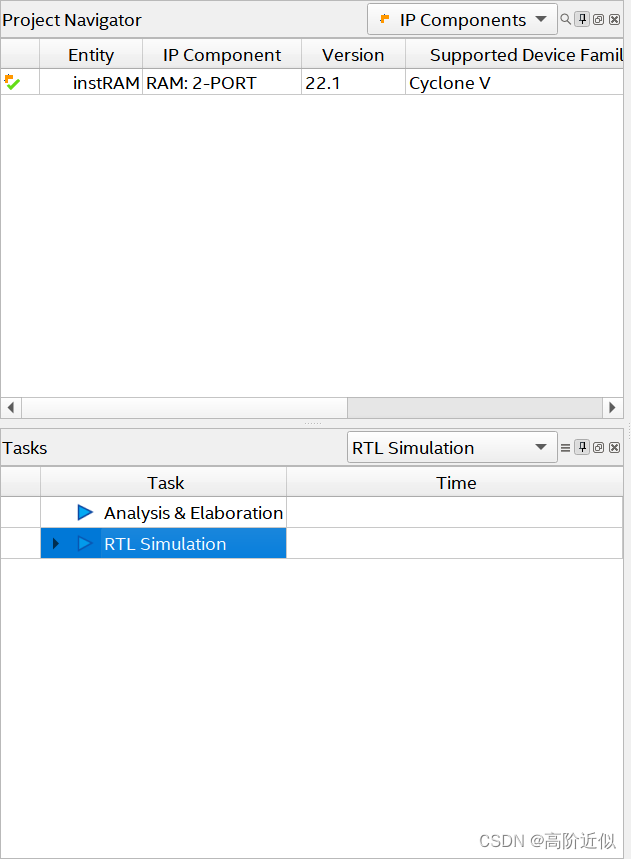

接下来点击下图中的 RTL Simualtion 即可开始模拟