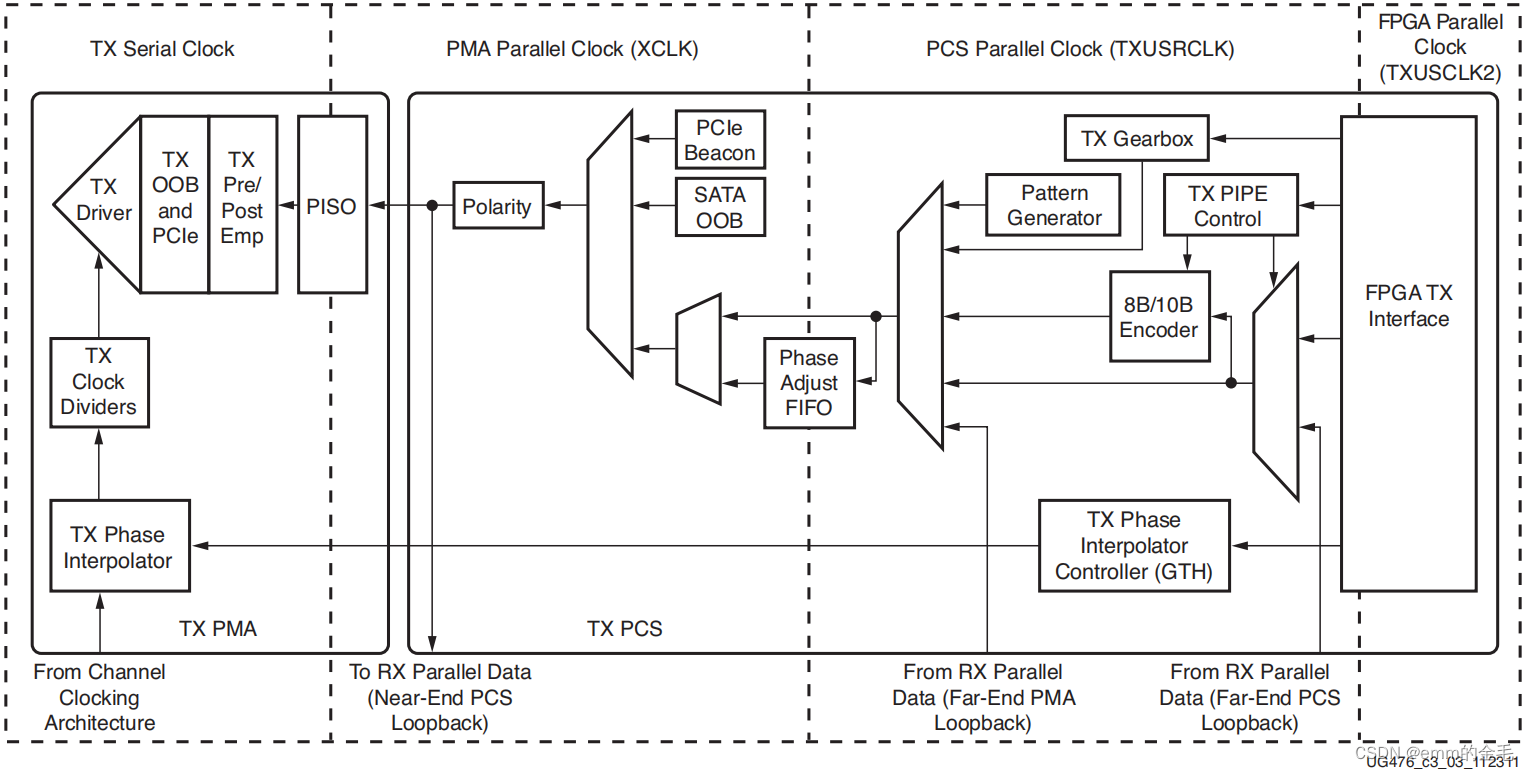

一、Transmitter 时钟分布

- XCLK:在使用TX buffer的模式下,XCLK来源于TXOUTCLK。在使用TX bypassing的模式下XCLK来源于TXUSERCLK。

- TXUSRCLK是GTX/GTH中PCS的内部逻辑时钟。

- TXUSRCLK2是GT Transceiver 用户侧逻辑时钟。

TXUSRCLK与TXUSRCLK2的关系

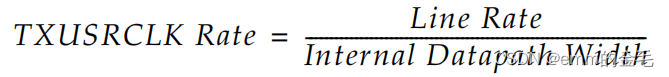

FPGA TX接口包括两个并行时钟: TXUSRCLK和TXUSRCLK2。TXUSRCLK是GTX/GTH发送端中PCS逻辑的内部时钟。TXUSRCLK所需的速率取决于GTXE2_CHANNEL/GTHE2_CHANNEL原语的内部数据路径宽度和GTX/GTH Transmitter 中TX线速率。

TXUSERCLK的时钟频率与线速率的关系如下:

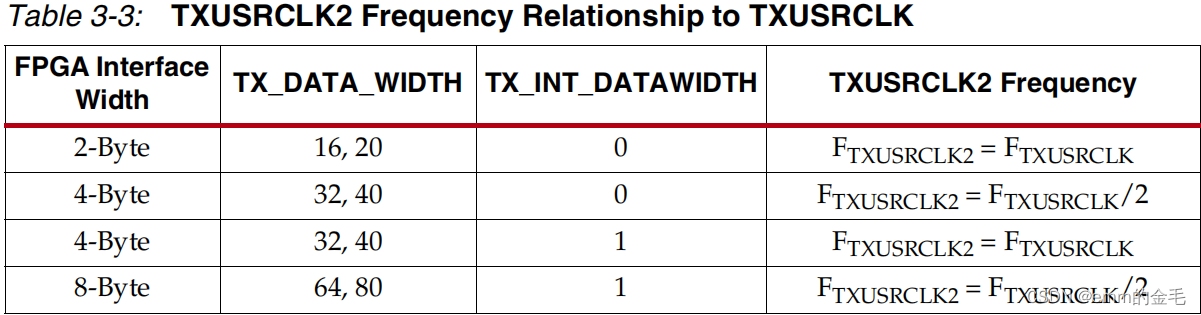

TXUSRCLK2是数据进入GT Transceiver TX一侧的同步时钟,TXUSRCLK2和TXUSRCLK具有基于TX_DATA_WIDTH(整数)和TX_INT_DATAWIDTH设置的固定速率关系。

(通过设置TX_INT_DATAWIDTH,可以选择7系列FPGA GTX/GTH收发器的内部数据宽度:2 Byte或者4Byte)。

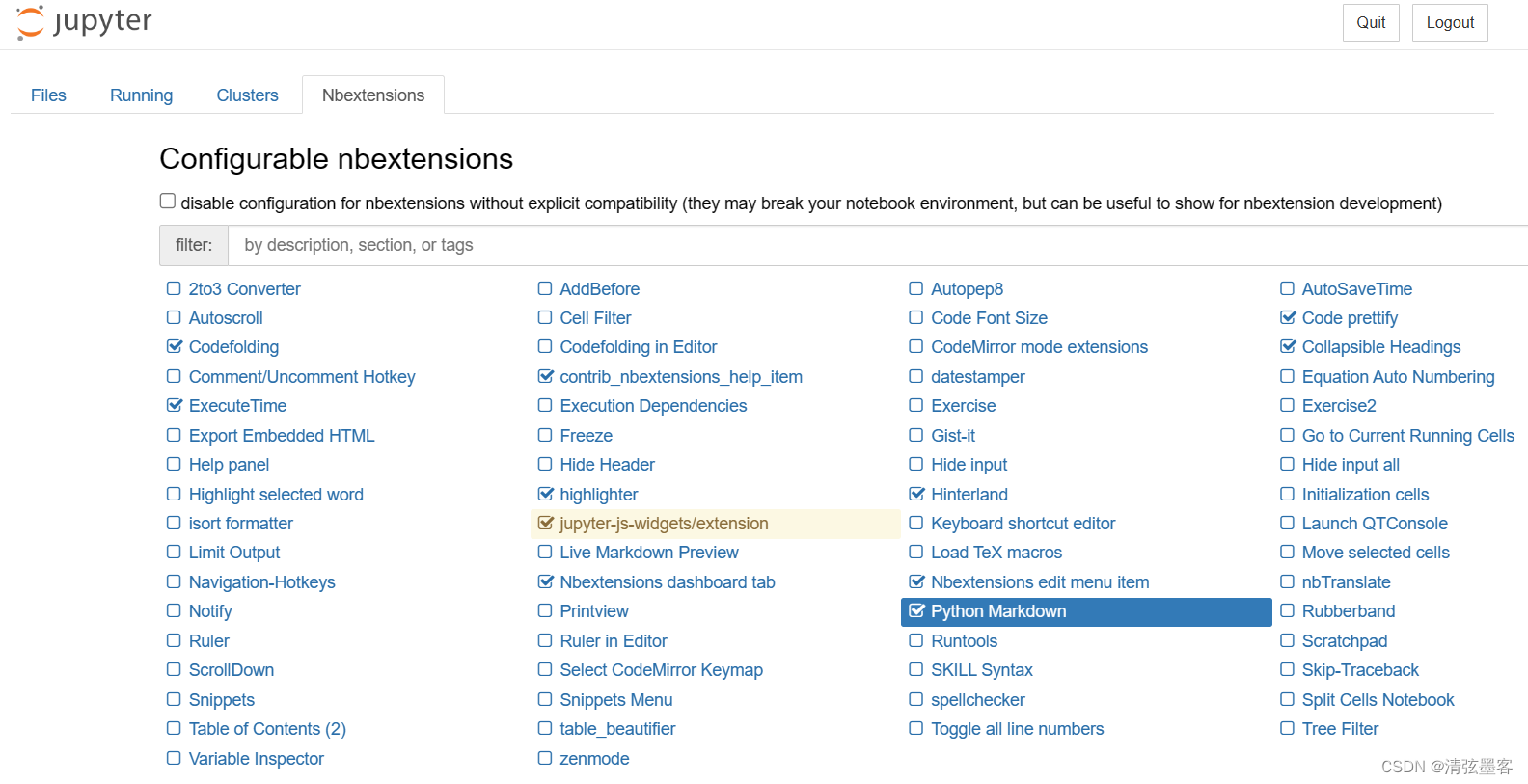

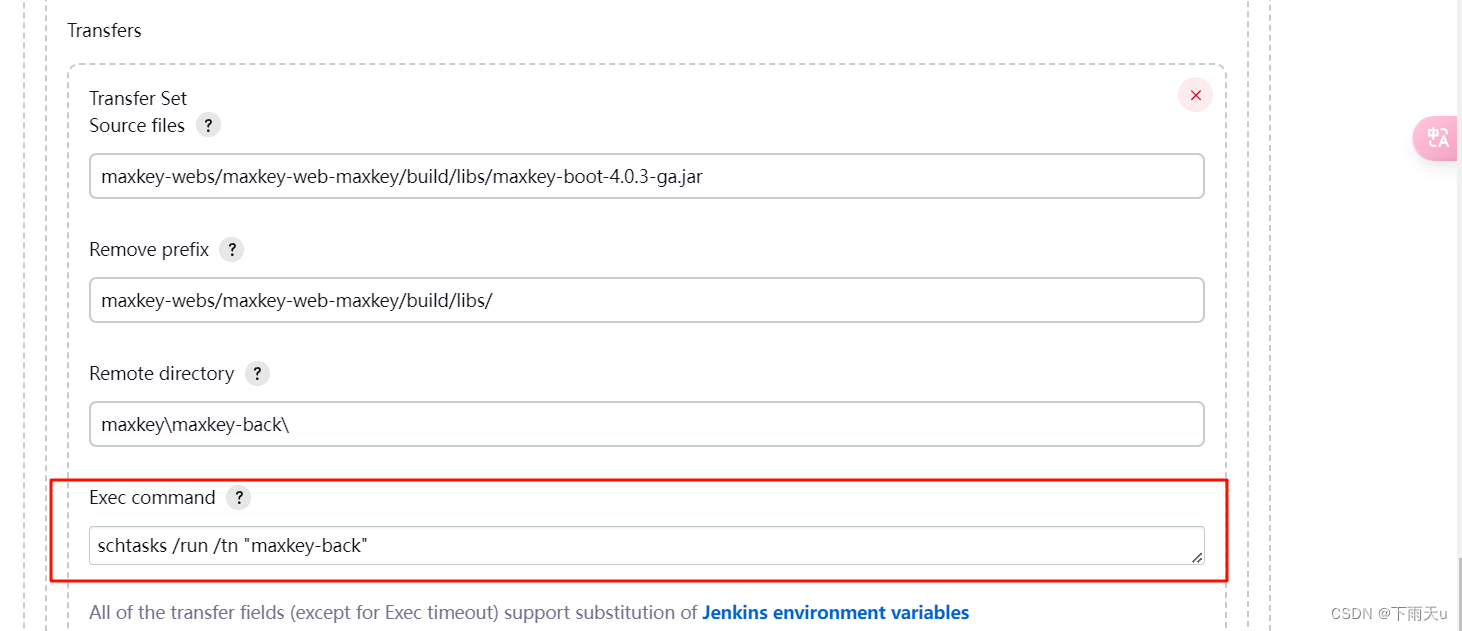

TXUSERCLK和TXUSERCLK2一般是通过TXOUTCLK产生,产生方式有如下几种:

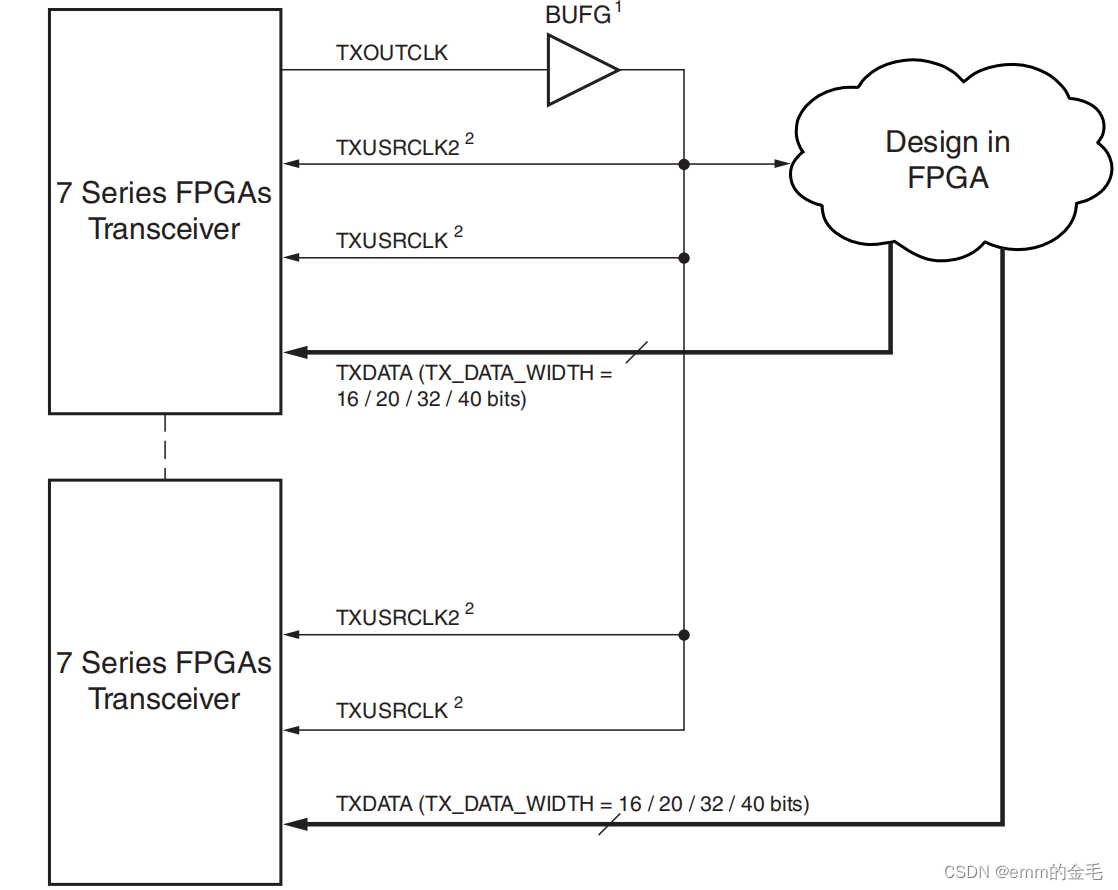

1、TXOUTCLK = TXUSRCLK = TXUSRCLK2

主要用于:

-

2-byte mode:TX_DATA_WIDTH = 16、20和TX_INT_DATWIDTH = 0

-

4-byte mode:TX_DATA_WIDTH = 32、40和TX_INT_DATWIDTH = 1

当选择多通道模式时,选择其中一个通道的TXOUTCLK作为主时钟去生成TXUSRCLK、TXUSRCLK2,这样可以节省BUFG资源。

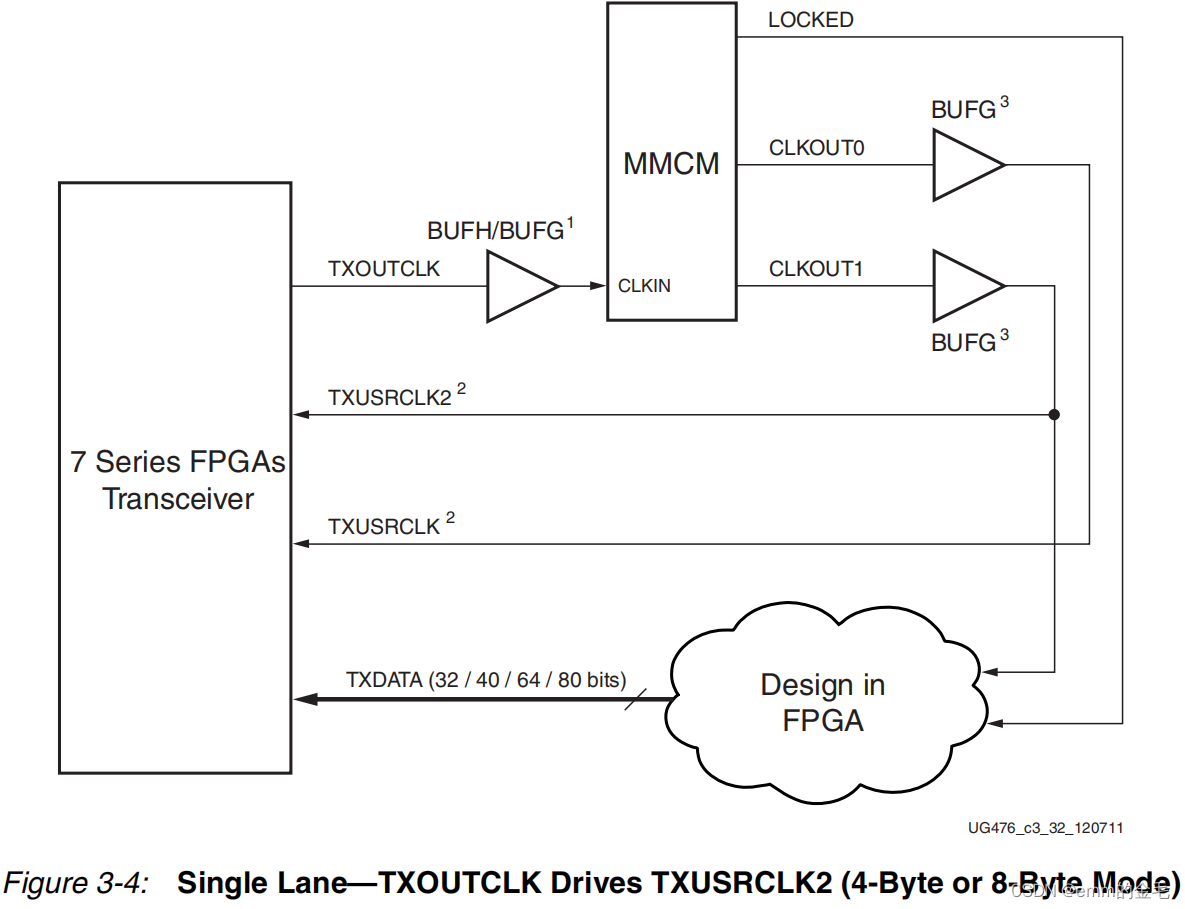

2、TXUSERCLK/2 = TXUSERCLK2

2、TXUSERCLK/2 = TXUSERCLK2

主要用于:

-

4-byte mode:TX_DATA_WIDTH = 32、40和TX_INT_DATWIDTH = 0

-

8-byte mode:TX_DATA_WIDTH = 64、80和TX_INT_DATWIDTH = 1

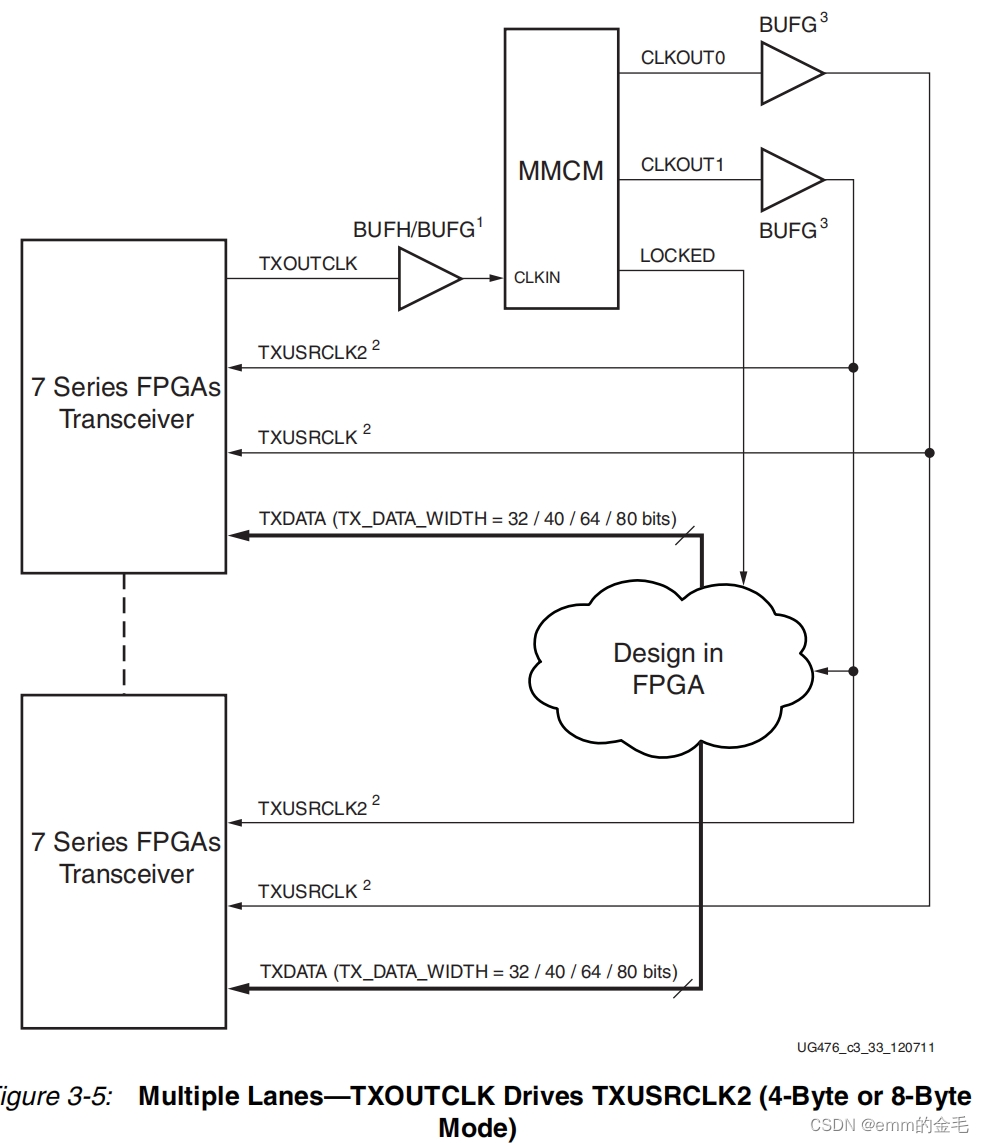

多通道模式如下:

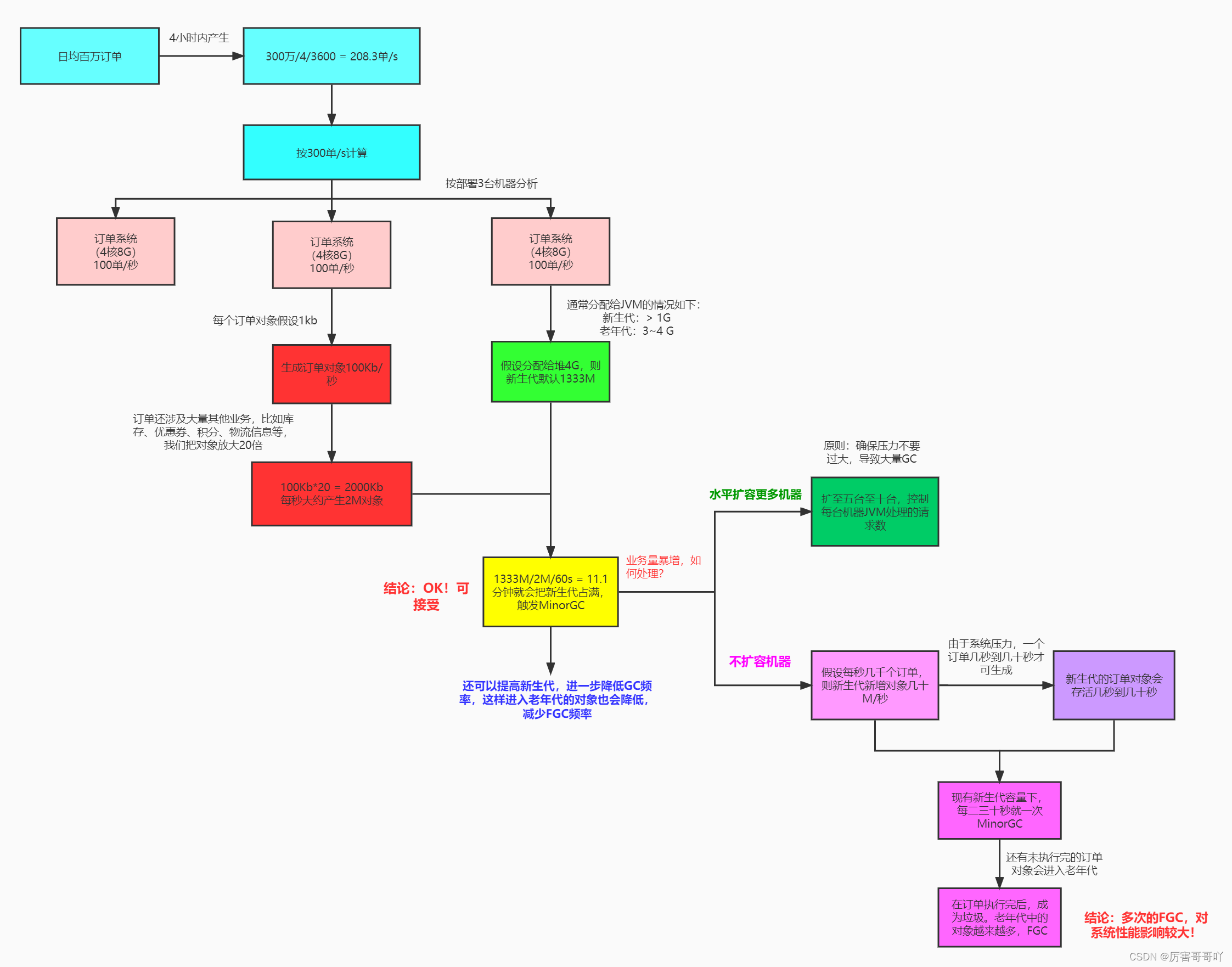

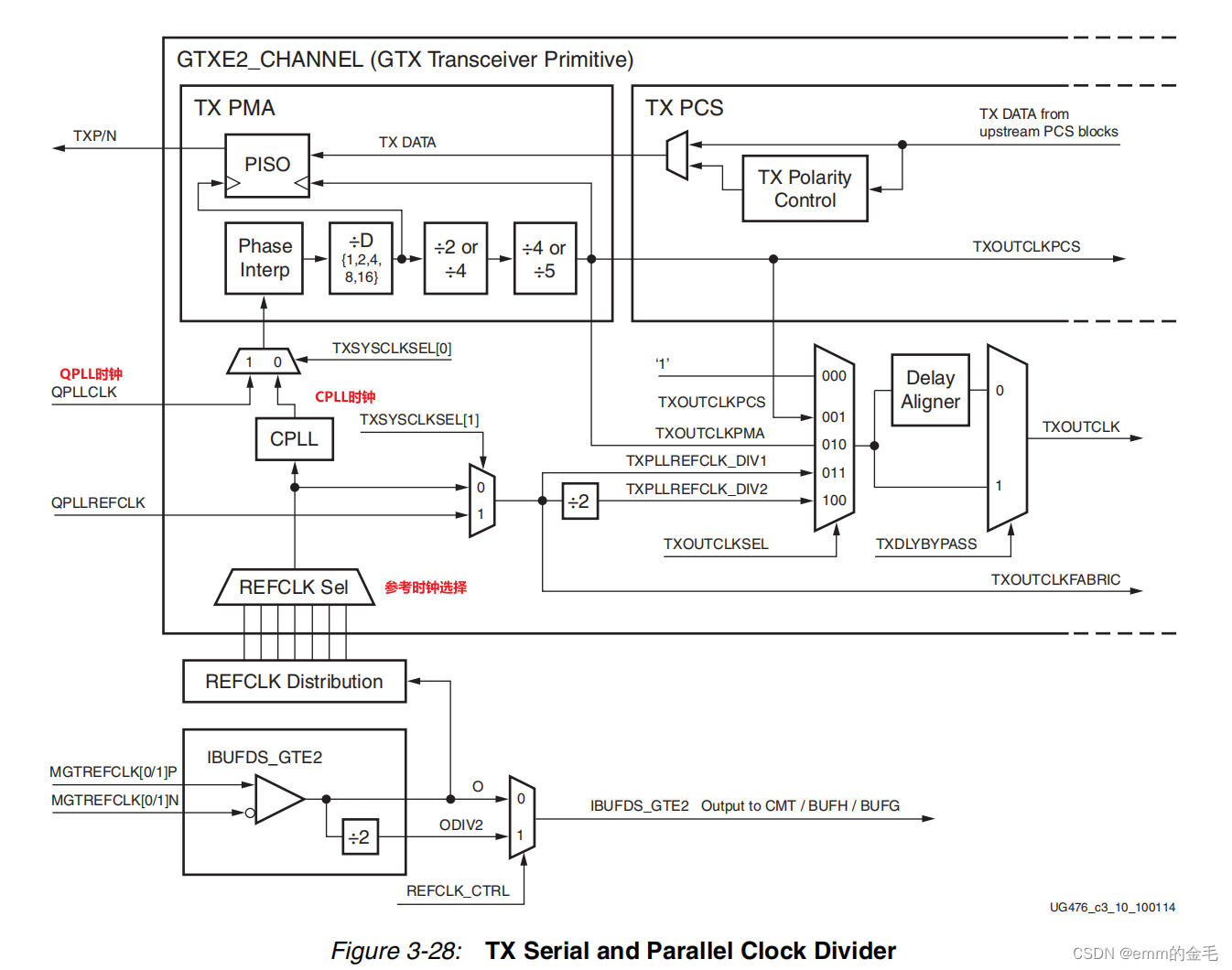

TXOUTCLK的产生

从上图可以看出TXOUCLK时钟的源时钟有如下几种:

- Quad 参考时钟

- QPLL产生的QPLLREFCLK

- CPLL时钟

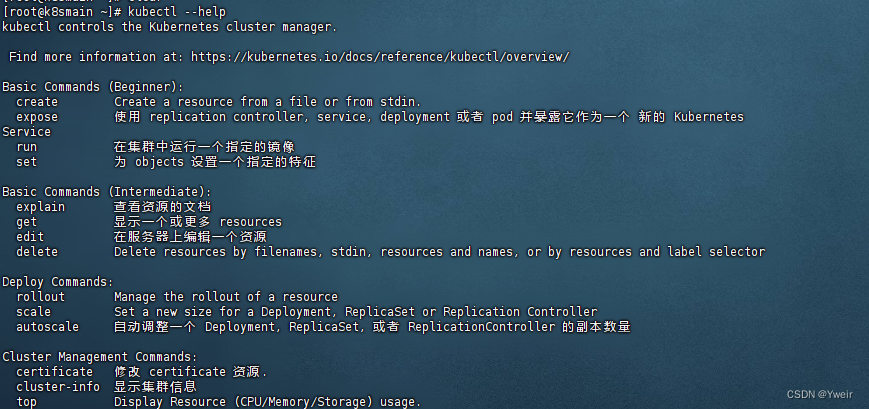

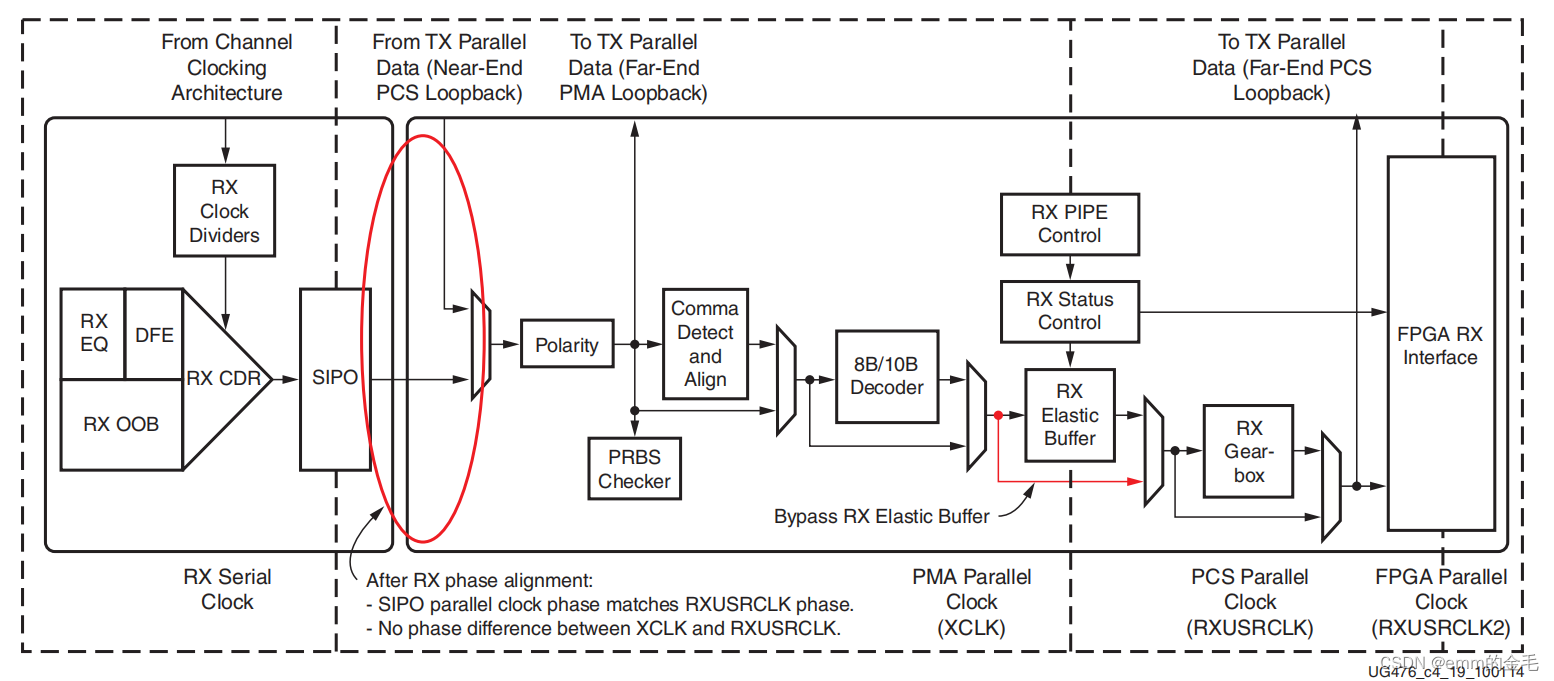

二、Receiver 时钟分布

主要有:

- 用户逻辑测的RXUSERCLK2

- PCS内部逻辑时钟RXUSERCLK

- PMA内部逻辑时钟XCLK。当使用RX elastic buffer时RX侧的XCLK主要于RX恢复的时钟,当绕过RX elastic buffe时,选择RXUSRCLK作为XCLK的源时钟。

- 用于串并转换的时钟:RX Serial Clock

RXUSRCLK和RXUSRCLK2的关系

FPGA RX接口包括两个并行时钟: RXUSRCLK和RXUSRCLK2。RXUSRCLK是GTX/GTH Transmitter中PCS逻辑的内部时钟。RXUSRCLK所需的速率取决于GTXE2_CHANNEL/GTHE2_CHANNEL原语的内部数据路径宽度和GTX/GTH Transmitter中RX线速率。

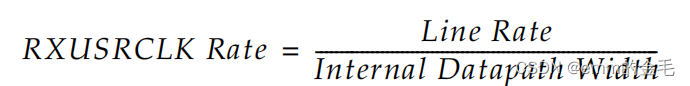

RXUSERCLK与线速率的关系如下:

RXUSRCLK2与RXUSRCLK之间也有一定的频率关系:

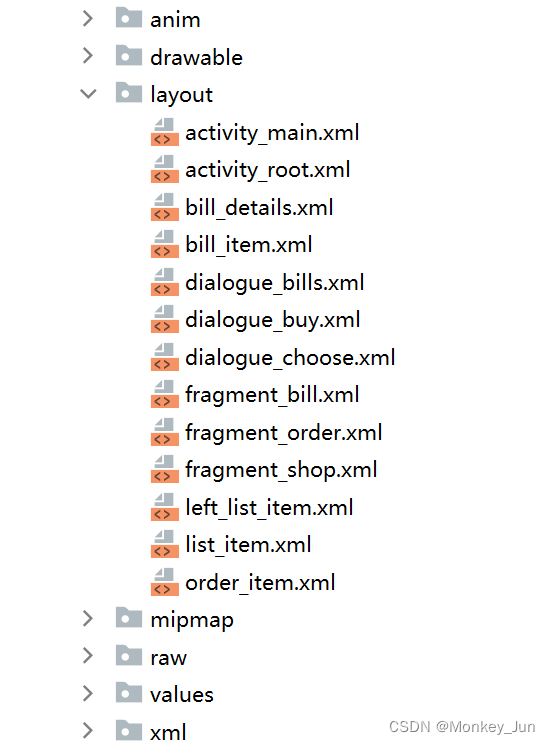

RXUSRCLK与RXUSRCLK2的来源有如下几种:

- 如果使用时钟矫正,那么RXUSRCLK与RXUSRCLK2可以通过RXOUTCLK和TXOUTCLK来获取

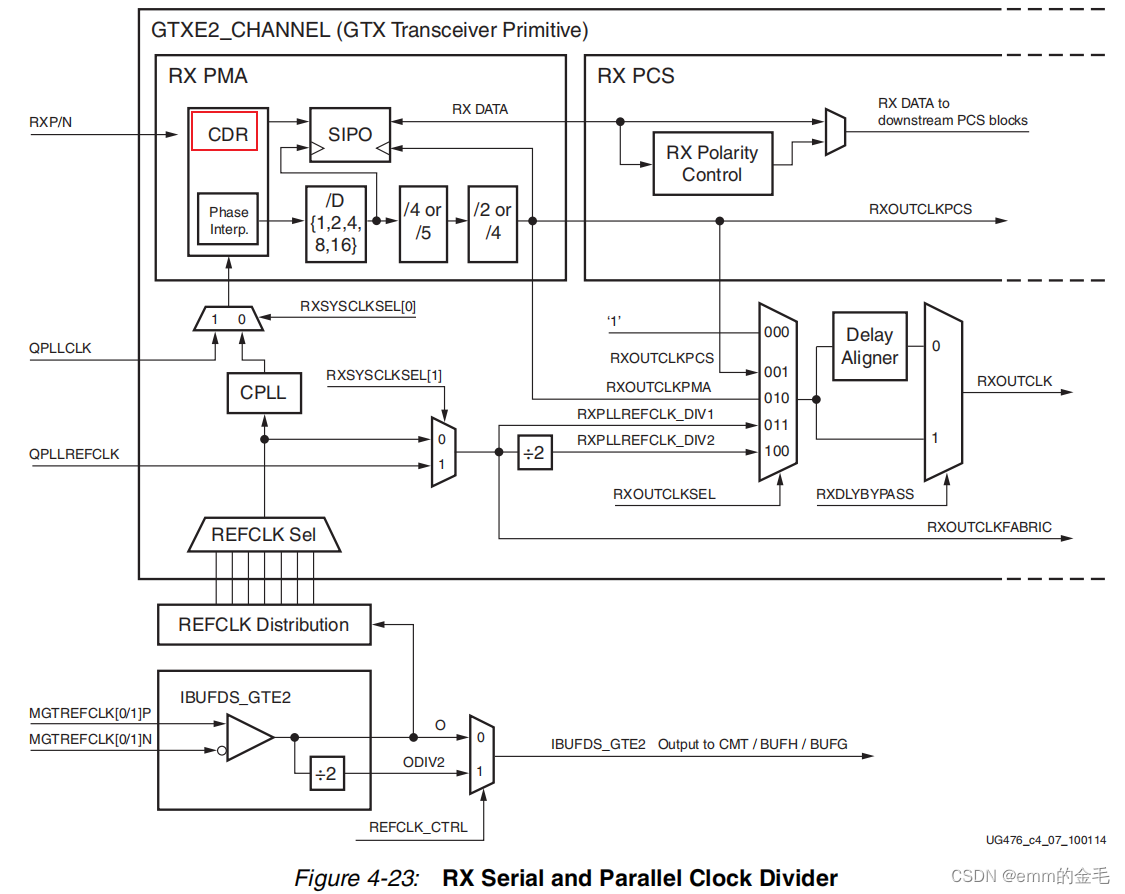

RXOUTCLK的产生

RXCLKOUT的来源如下:

- Quad 的REFCLK

- QPLLREFCLK

- QPLLCLK、CPLLCLK

- CDR 恢复出来的时钟