目录

wire型

reg型

Memory型

wire型

wire 类型变量,也叫网络类型变量,用于结构实体之间的物理连接,如门与门之间,不能储存值,用连续赋值语句 assign 赋值,定义为

wire [n-1:0] a ;

其中 n 代表位宽,如定义

wire a ; assign a = b ;

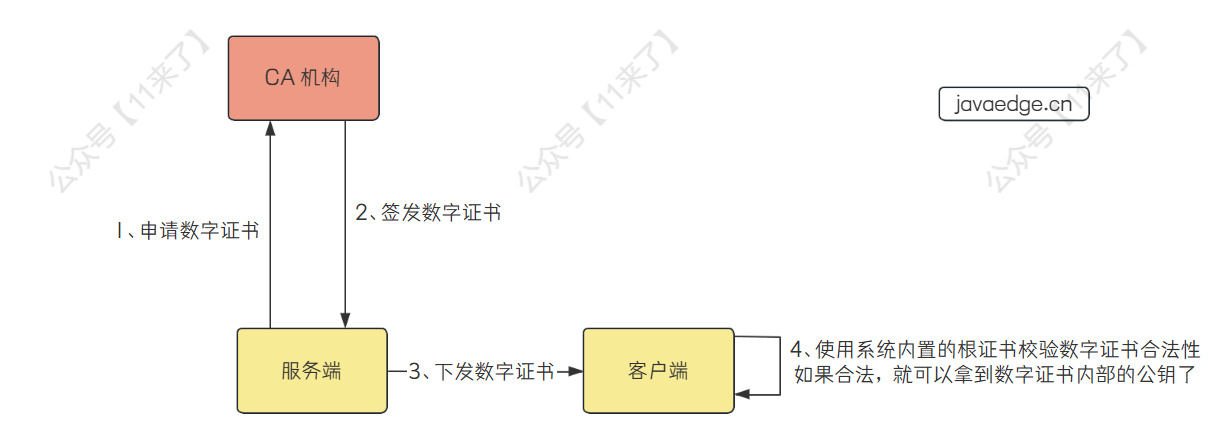

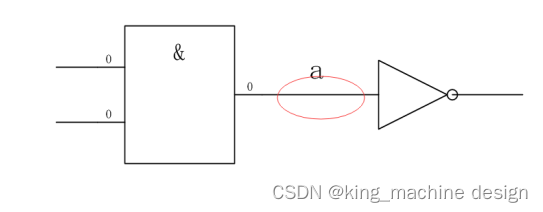

是将 b 的结点连接到连线 a 上。如下图所示,两个实体之间的连线即是 wire 类型变量。

reg型

reg 类型变量,也称为寄存器变量,可用来储存值,必须在 always 语句里使用。其定义为

reg [n-1:0] a ;表示 n 位位宽的寄存器,如

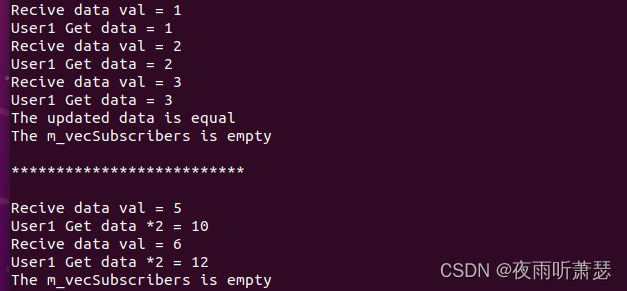

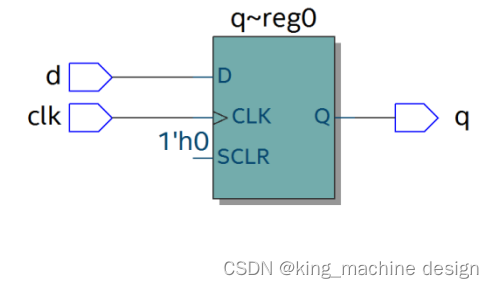

reg [7:0] a; 表示定义 8 位位宽的寄存器 a。如下所示定义了寄存器 q,生成的电路为时序逻辑,图为其结构,为 D 触发器。

(CSDN代码块不支持Verilog,代码复制到notepad++编辑器中,语言选择Verilog,看得更清楚)

module top(d, clk, q) ;

input d ;

input clk ;

output reg q ;

always @(posedge clk)

begin

q <= d ;

end

endmodule

也可以生成组合逻辑,如数据选择器,敏感信号没有时钟,定义了

reg Mux

,最终生成电路为组合逻辑。

module top(a, b, c, d, sel, Mux) ;

input a ;

input b ;

input c ;

input d ;

input [1:0] sel ;

output reg Mux ;

always @(sel or a or b or c or d)

begin

case(sel)

2'b00 : Mux = a ;

2'b01 : Mux = b ;

2'b10 : Mux = c ;

2'b11 : Mux = d ;

endcase

end

endmodule

Memory型

可以用

memory

类型来定义

RAM,ROM

等存储器,其结构为

reg [n-1:0] 存储器名[m-1:0];意义为 m 个 n 位宽度的寄存器。例如,

reg [7:0] ram [255:0];

表示定义了 256 个 8 位寄存器,256 也即是存储器的深度,8 为数据宽度。