FSMC控制 TFTLCD的寄存器配置

- 异步模式 A控制 TFTLCD

- FSMC寄存器配置

- ILI9341电平持续时间要求

- 参考

异步模式 A控制 TFTLCD

LCD以ILI9341为例

FSMC寄存器配置

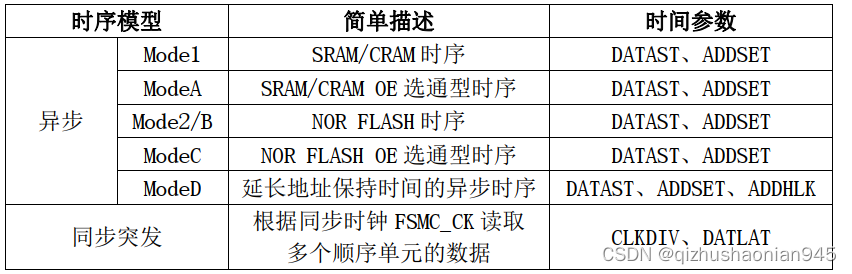

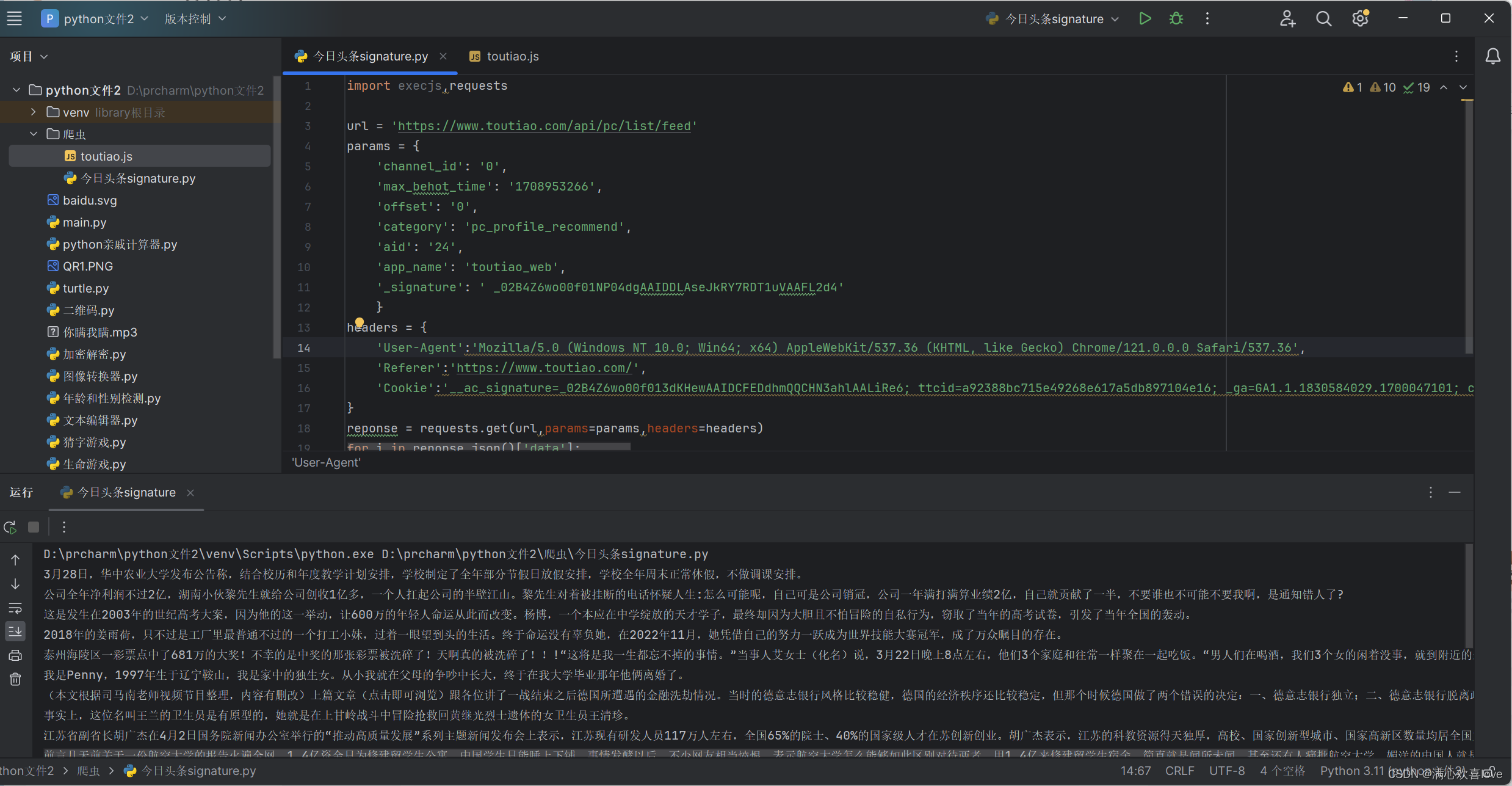

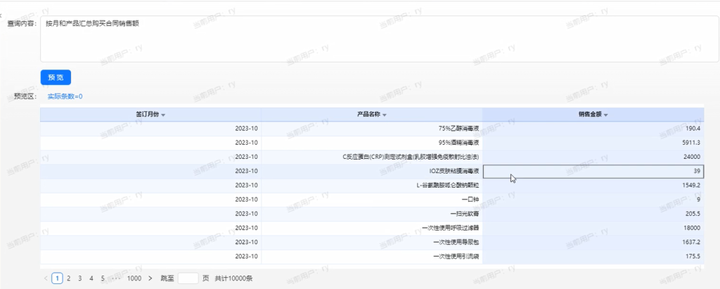

对于异步突发访问方式, FSMC 主要设置 3 个时间参数:地址建立时间(ADDSET)、 数据

建立时间(DATAST)和地址保持时间(ADDHLD)。 FSMC 综合了 SRAM/ ROM、 PSRAM 和 NOR

Flash 产品的信号特点,定义了 4 种不同的异步时序模型。选用不同的时序模型时,需要设置不

同的时序参数

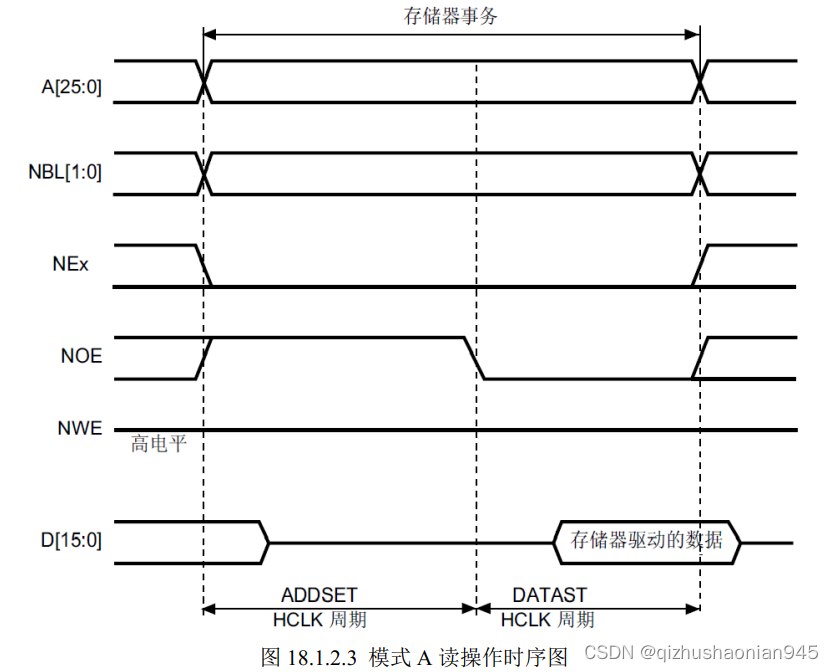

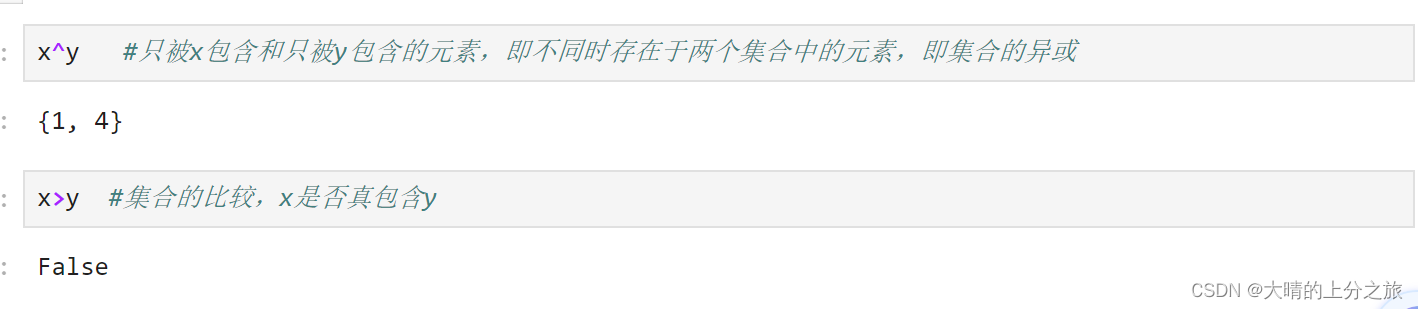

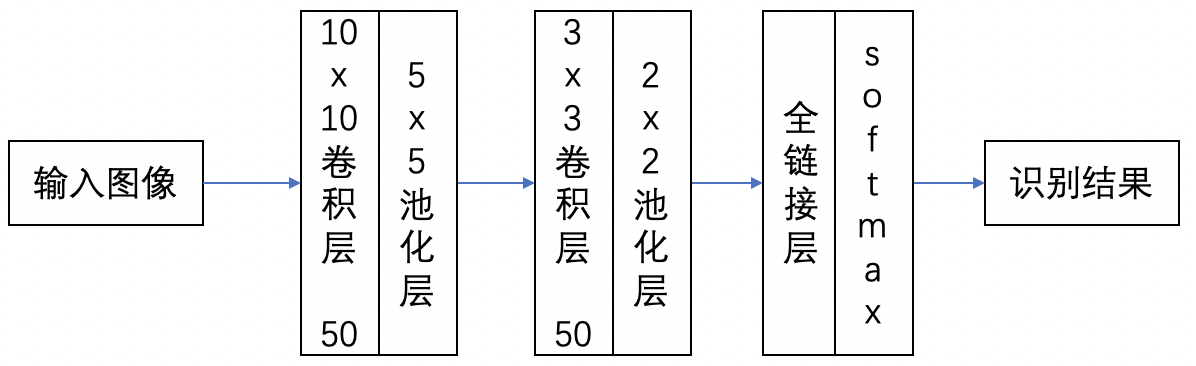

使用异步模式 A(ModeA)方式来控制 TFTLCD,模式 A 的读操作时序如图

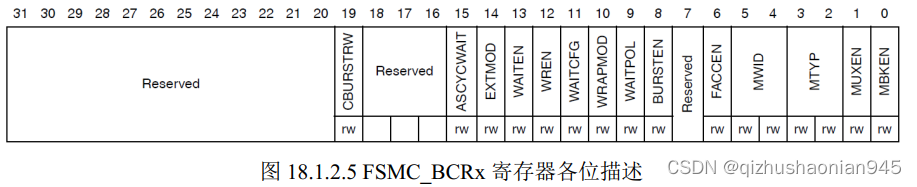

SRAM/NOR 闪存片选控制寄存器: FSMC_BCRx(x=1~4)

EXTMOD:扩展模式使能位,也就是是否允许读写不同的时序,需要读

写不同的时序,故该位需要设置为 1。

设置了 EXTMOD 位,则有两个时序寄存器分别对应读(本寄存器)和写操作(FSMC_BWTRx 寄存器)

WREN:写使能位。我们需要向 TFTLCD 写数据,故该位必须设置为 1。

MWID[1:0]:存储器数据总线宽度。 00,表示 8 位数据模式; 01 表示 16 位数据模式; 10

和 11 保留。我们的 TFTLCD 是 16 位数据线,所以设置 WMID[1:0]=01。

MTYP[1:0]:存储器类型。 00 表示 SRAM、 ROM; 01 表示 PSRAM; 10 表示 NOR FLASH;11

保留。前面提到,我们把 TFTLCD 当成 SRAM 用,所以需要设置 MTYP[1:0]=00。

MBKEN:存储块使能位。这个容易理解,我们需要用到该存储块控制 TFTLCD,MBKEN=1

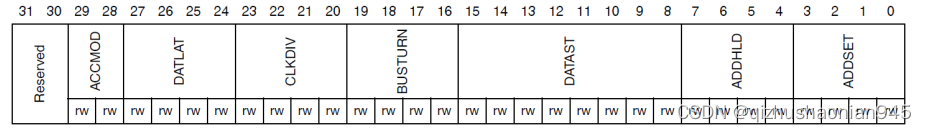

SRAM/NOR 闪存片选时序寄存器: FSMC_BTRx(x=1~4)

ACCMOD[1:0]:访问模式。 00 访问模式 A;同理 01 表示 B; 10 表示 C;11 表示 D,本章我们用到模式 A,故设置为 00。

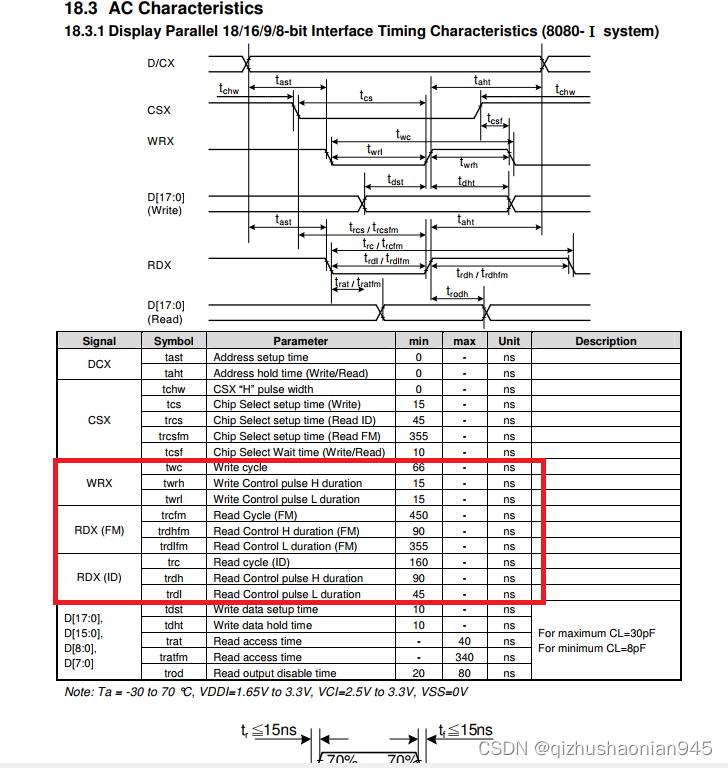

DATAST[7:0]:数据保持时间。 0 为保留设置,其他设置则代表保持时间为: DATAST 个

HCLK 时钟周期,最大为 255 个 HCLK 周期。对 ILI9341 来说,其实就是 RD 低电平持续时间,

一般为 355ns。而一个 HCLK 时钟周期为 6ns 左右(1/168Mhz),为了兼容其他屏,我们这里设

置 DATAST 为 60,也就是 60 个 HCLK 周期,时间大约是 360ns。

ADDSET[3:0]:地址建立时间。其建立时间为: ADDSET 个 HCLK 周期,最大为 15 个 HCLK

周期。对 ILI9341 来说,这里相当于 RD 高电平持续时间,为 90ns,我们设置 ADDSET 为 15,

即 15*6=90ns。

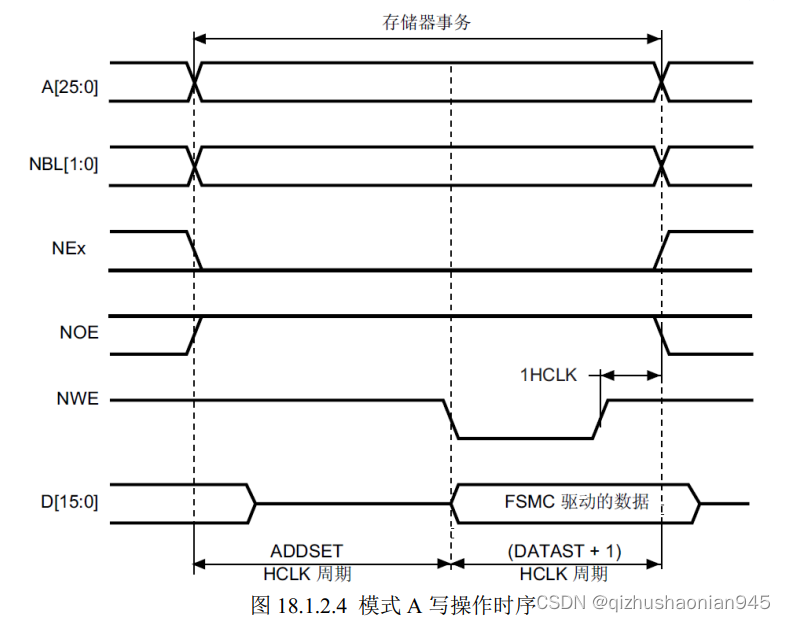

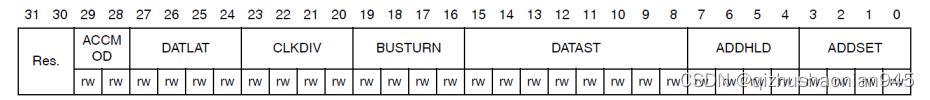

SRAM/NOR 闪写时序寄存器: FSMC_BWTRx(x=1~4)

ACCMOD、 DATAST

和 ADDSET 这三个设置。这三个设置的方法同 FSMC_BTRx 一模一样,只是这里对应的是写

操作的时序, ACCMOD 设置同 FSMC_BTRx 一模一样,同样是选择模式 A,另外 DATAST 和

ADDSET 则对应低电平和高电平持续时间,对 ILI9341 来说,这两个时间只需要 15ns 就够了,

比读操作快得多。所以我们这里设置 DATAST 为 2,即 3 个 HCLK 周期,时间约为 18ns。然后

ADDSET 设置为 3,即 3 个 HCLK 周期,时间为 18ns。

FSMC_BCRx 和 FSMC_BTRx,组合成 BTCR[8]寄存器组,他们的对应关系如下:

BTCR[0]对应 FSMC_BCR1, BTCR[1]对应 FSMC_BTR1

BTCR[2]对应 FSMC_BCR2, BTCR[3]对应 FSMC_BTR2

BTCR[4]对应 FSMC_BCR3, BTCR[5]对应 FSMC_BTR3

BTCR[6]对应 FSMC_BCR4, BTCR[7]对应 FSMC_BTR4

FSMC_BWTRx 则组合成 BWTR[7],他们的对应关系如下:

BWTR[0]对应 FSMC_BWTR1, BWTR[2]对应 FSMC_BWTR2,

BWTR[4]对应 FSMC_BWTR3, BWTR[6]对应 FSMC_BWTR4,

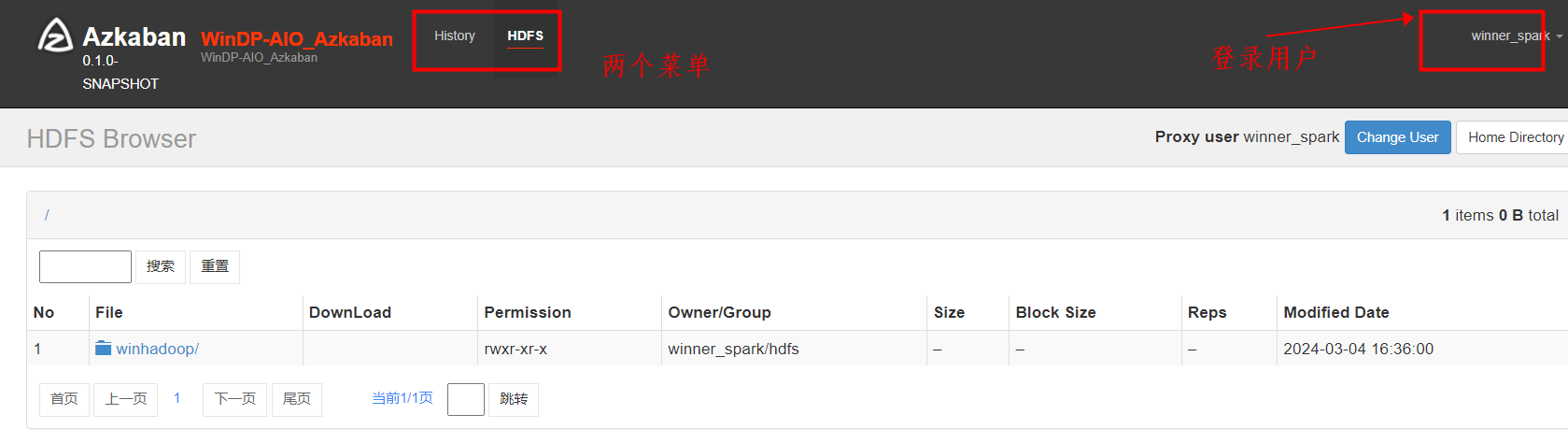

ILI9341电平持续时间要求

参考

STM32F4开发指南-库函数版本_V1.2

ILI9341_DS

![[lesson10]C++中的新成员](https://img-blog.csdnimg.cn/direct/21cd8d94100a4f12af69deeb82de1e1c.png#pic_center)