一. 简介

正点原子的开发板 ALPHA开发板,有线网络硬件方案所使用的也是最常用的一种方案,IMX6ULL芯片内部是自带 MAC网络芯片的,所以,也就是采用 "SOC内部集成网络MAC外设+ PHY网络芯片方案"。

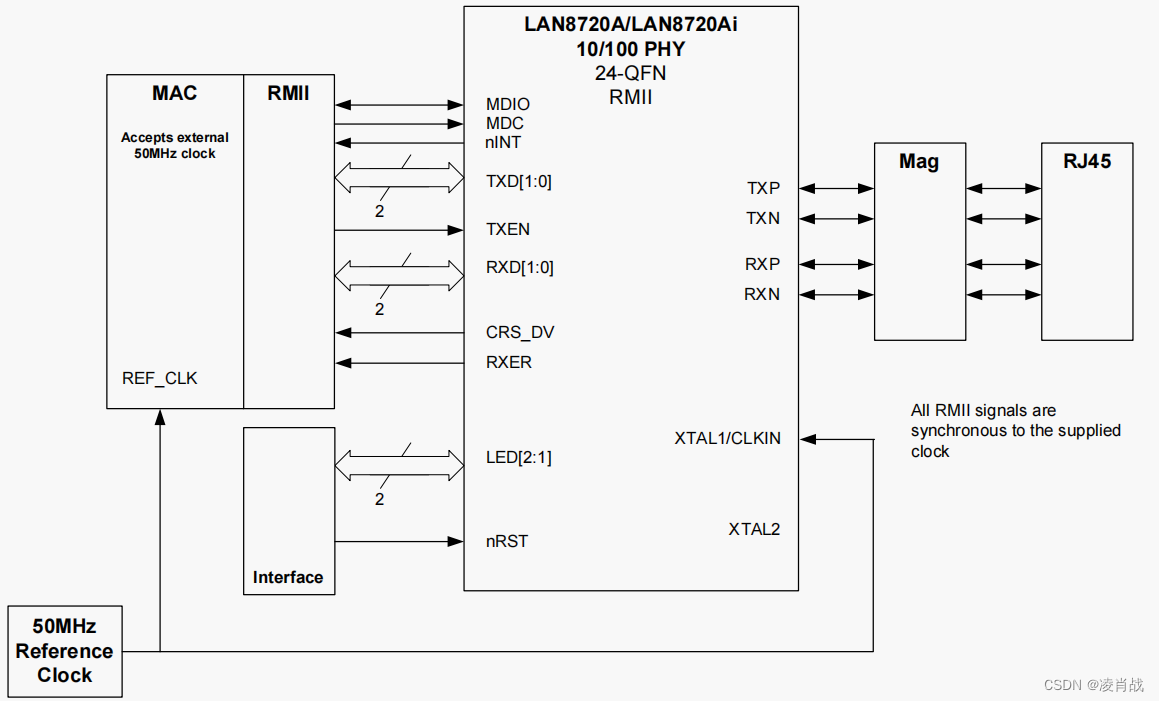

ALPHA开发板使用的PHY网络芯片是 LAN8720,本文简单了解一下 LAN8720芯片特性与常用的寄存器。

二. ALPHA开发板上PHY网络芯片LAN8720

虽然本文讲解的是

LAN8720A

这颗

PHY

网络芯片,但是前面说了,

IEEE

规定了

PHY

的前

16

个

寄存器的功能(即所有的 PHY芯片的前16个寄存器的功能必须要保持统一),因此,如果你所使用的板子用的其他厂家的

PHY

芯片,也是可以看本文。

1. LAN8720A 简介

LAN8720A

是低功耗的

10/100M

单以太网

PHY

层芯片,可应用于机顶盒、网络打印机、嵌入式通信设备、

IP

电话等领域。

I/O

引脚电压符合

IEEE802.3-2005

标准。

LAN8720A

支持通

过

RMII

接口与以太网

MAC

层通信,内置

10-BASE-T/100BASE-TX

全双工传输模块,支持

10Mbps

和

100Mbps

。

LAN8720A

可以通过自协商的方式选择与目的主机最佳的连接方式

(

速度

和双工模式

)

。支持

HP Auto-MDIX

自动翻转功能,无需更换网线即可将连接更改为直连或交叉

连接。

LAN8720A

的主要特点如下:

· 高性能的

10/100M

以太网传输模块

· 支持

RMII

接口以减少引脚数

· 支持全双工和半双工模式

· 两个状态

LED

输出

· 可以使用

25M

晶振以降低成本

· 支持自协商模式

· 支持

HP Auto-MDIX

自动翻转功能

· 支持

SMI

串行管理接口

· 支持

MAC

接口

2. LAN8720A 中断管理

LAN8720A

的器件管理接口支持非

IEEE 802.3

规范的中断功能。当一个中断事件发生并且相应事件的中断位使能,

LAN8720A

就会在

nINT(14

脚

)

产生一个低电平有效的中断信号。

LAN8720A

的中断系统提供两种中断模式:主中断模式和复用中断模式。

主中断模式是默认中

断模式,

LAN8720A

上电或复位后就工作在主中断模式,当模式控制

/

状态寄存器

(

十进制地址

为

17)

的

ALTINT

位为

0

时,

LAN8720A

工作在主模式,当

ALTINT

位为

1

时,工作在复用中断模

式。

正点原子的

ALPHA

开发板虽然讲

LAN8720A

的中断引脚连接到了

I.MX6ULL

上,但是并

没有使用中断功能,关于中断的具体用法可以参考

LAN8720A

数据手册的

29~30

页。

3. PHY 地址设置

MAC

层通过

MDIO/MDC

总线对

PHY

进行读写操作,

MDIO

最多可以控制

32

个

PHY

芯片,通过不同的

PHY

芯片地址来对不同的

PHY

操作。

LAN8720A

通过设置

RXER/PHYAD0

引脚来设置其

PHY

地址,默认情况下为

0

,其地址设置如下表所

示。

正点原子

ALPHA

开发板的

ENET1

网络的

LAN8720A

上的

RXER/PHYAD0

引脚为默认状态

(

网络硬件原理图上有个

10K

下拉,但是没有焊接

)

,因此,

ENET1

上的

LAN8720A

地址为

0

。

ENET2

网络上的

LAN8720A

上的

RXER/PHYAD0

引脚接了个

10K

上拉电阻,因此,

ENET2

上的

LAN8720A

地址为

1

。

4. nINT/REFCLKO 配置

nINTSEL

引脚

(2

号引脚

)

用于设置

nINT/REFCLKO

引脚

(14

号引脚

)

的功能。

nINTSEL

配置如下表

所示。

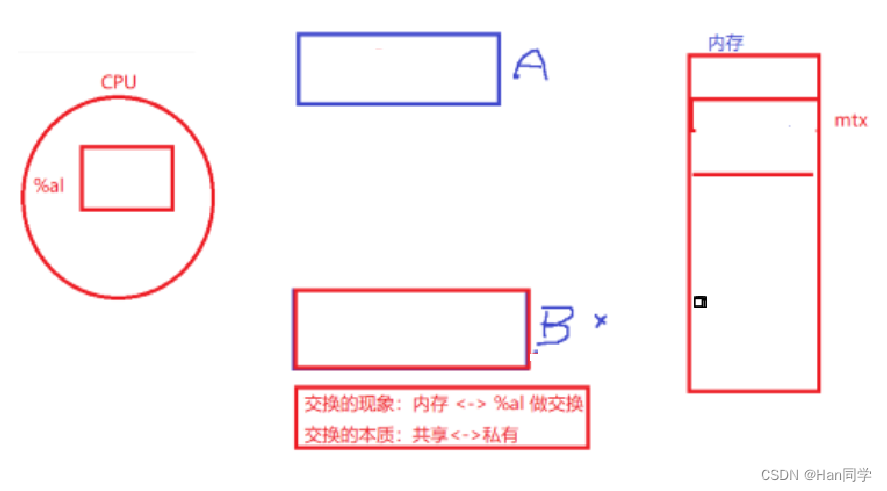

对于正点原子的 ALPHA 开发板的两个 LAN8720A 而言,全都工作在默认的 REF_CLK In 模式下。当 LAN8720A 工作在 REF_CLK In 模式时,50MHz 的外部时钟信号应接到 LAN8720 的 XTAL1/CLKIN 引脚(5 号引脚)上,如下图所示:

为了降低成本,LAN8720A 可以从外部的 25MHz 的晶振中产生 REF_CLK 时钟。到要使用此功能时应工作在 REF_CLK Out 模式时。当工作在 REF_CLO Out 模式时 REF_CLK 的时钟源 如下图所示。

前面说了,正点原子的

ALPHA

开发板工作在

REF_CLK In

模式下,因此需要外部

50MHz

时钟信号。

I.MX6ULL

有专用的网络时钟引脚,因此,

ALPHA

开发板是通过

I.MX6ULL

的

ENET1_REF_CLK

和

ENET2_REF_CLK

这两个网络时钟引脚,来为

LAN8720A

提供

50MHz

的

时钟。

接下来了解一下 LAN8720芯片(PHY网络芯片)的几个常用的寄存器。