文章目录

- 一、UART接收模块误码率

- 二、接收时钟动态纠正方法

- 2.1、过采样

- 2.2、上板效果

一、UART接收模块误码率

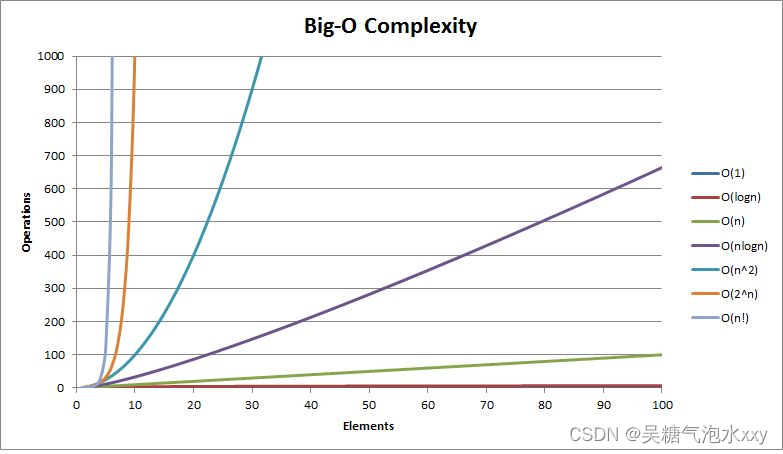

由于发送端和接收端存在一定的频率误差,随着时间的推移,累计误差不断增加,从而产生亚稳态现象,会导致误码,因此需要对时钟做动态纠正

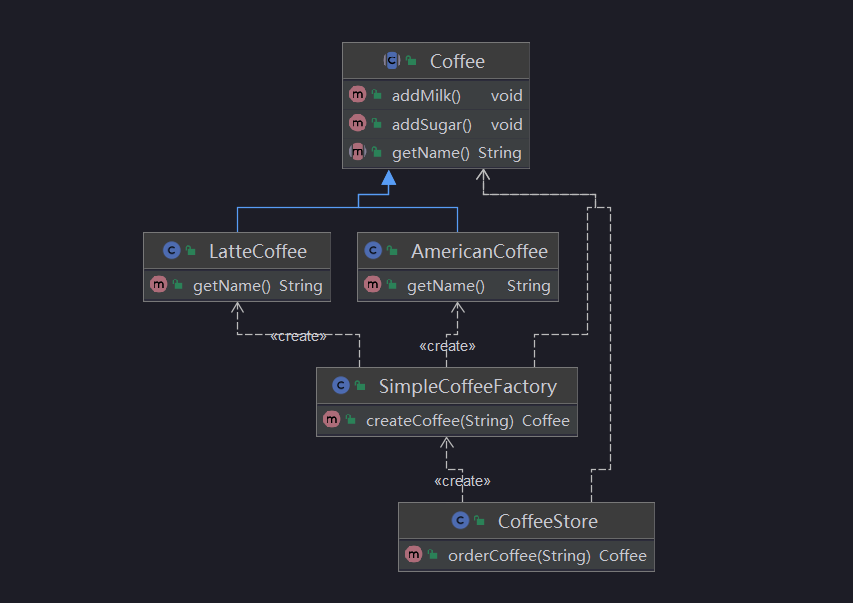

二、接收时钟动态纠正方法

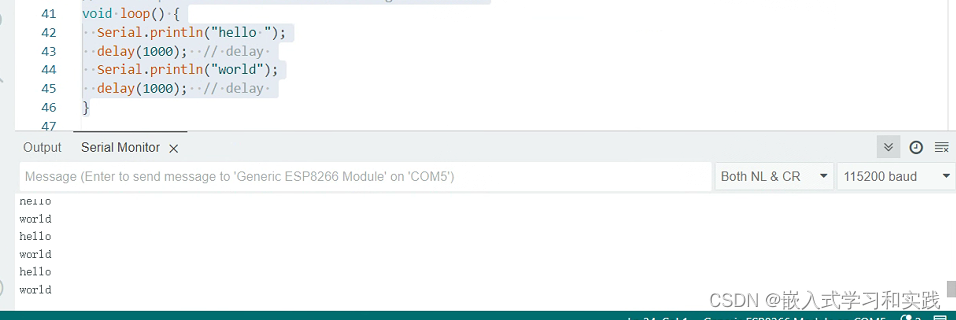

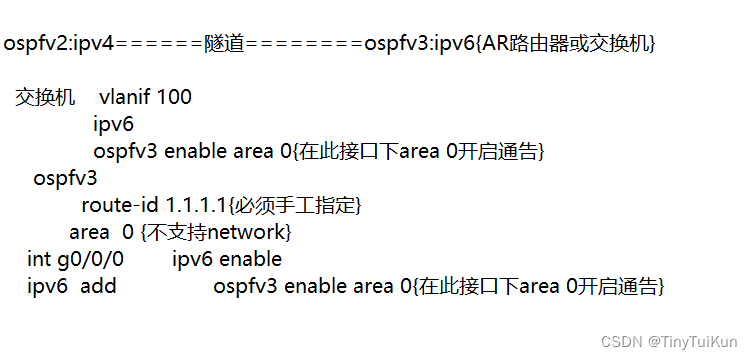

接收模块当识别到起始位的时候,开始产生接收时钟,接收时钟的上升沿处于数据线正中间,因此每次接收新数据的时候,接收时钟都在数据稳定的中间附近进行采样,并且用的都是新时钟,规避累计误差。

2.1、过采样

完整代码详见:https://github.com/shun6-6/UART_Pro

注:代码为本人通过学习FPGA奇哥系列网课进行自主编写

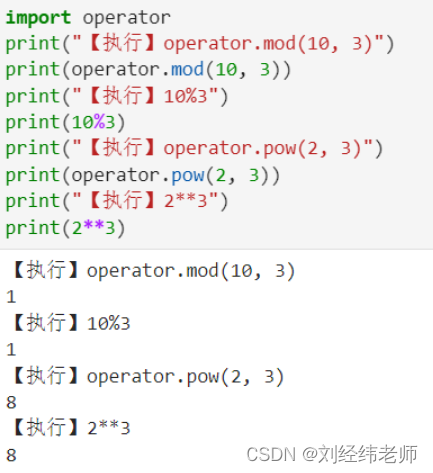

想要识别起始位下降沿,需要采用过采样,即使用大于波特率的时钟进行识别起始位。

r_uart_rx_rst 为时钟分频模块的复位信号,当识别到起始位时,r_rx_overlock会拉低,复位取消,开始产生接收时钟,当一次数据接收完成时重新复位。

r_uart_overvalue 对接收的异步数据进行打拍,并以此判断起始位下降沿

r_rx_overlock 拉高表示当前已经已经识别到起始位

always@(posedge i_clk or posedge i_rst)begin

if(i_rst)

r_uart_rx_rst <= 1'd1;

else if(!w_usr_rx_valid && r_usr_rx_valid_1d)

r_uart_rx_rst <= 1'd1;

else if(r_rx_overlock)

r_uart_rx_rst <= 1'd0;

else

r_uart_rx_rst <= r_uart_rx_rst;

end

always@(posedge i_clk or posedge i_rst)begin

if(i_rst)

r_uart_overvalue <= 'd0;

else if(!r_rx_overlock)

r_uart_overvalue <= {r_uart_overvalue[1:0] , i_uart_rx};

else

r_uart_overvalue <= 3'b111;

end

always@(posedge i_clk or posedge i_rst)begin

if(i_rst)

r_uart_overvalue_1d <= 'd0;

else

r_uart_overvalue_1d <= r_uart_overvalue;

end

always@(posedge i_clk or posedge i_rst)begin

if(i_rst)

r_rx_overlock <= 'd0;

else if(!w_usr_rx_valid && r_usr_rx_valid_1d)

r_rx_overlock <= 'd0;

else if(r_uart_overvalue == 3'b000 && r_uart_overvalue_1d != 3'b000)

r_rx_overlock <= 1'b1;

else

r_rx_overlock <= r_rx_overlock;

end

always@(posedge i_clk or posedge i_rst)begin

if(i_rst)

r_usr_rx_valid_1d <= 'd0;

else

r_usr_rx_valid_1d <= w_usr_rx_valid;

end

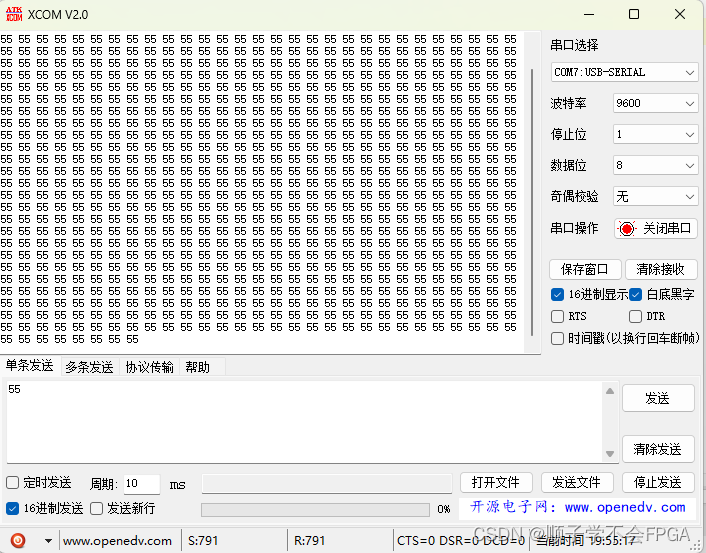

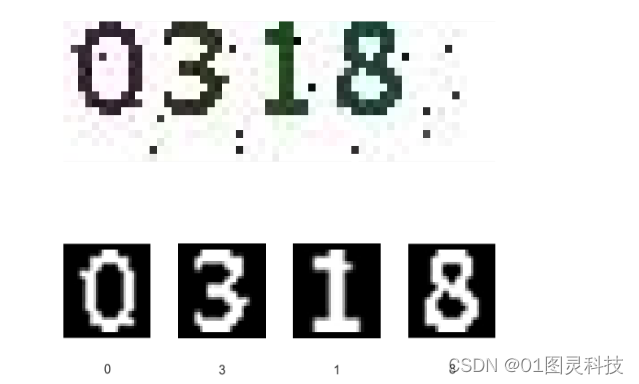

2.2、上板效果

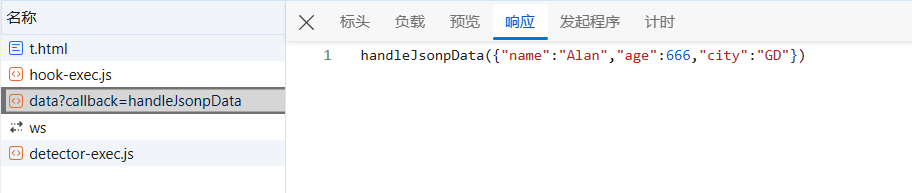

误码率几乎为0