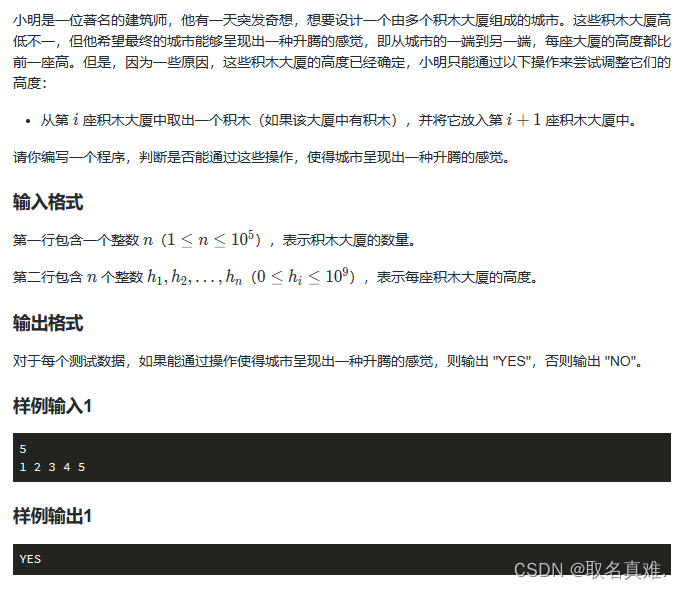

FPGA开发之libero模块实例化详细步骤

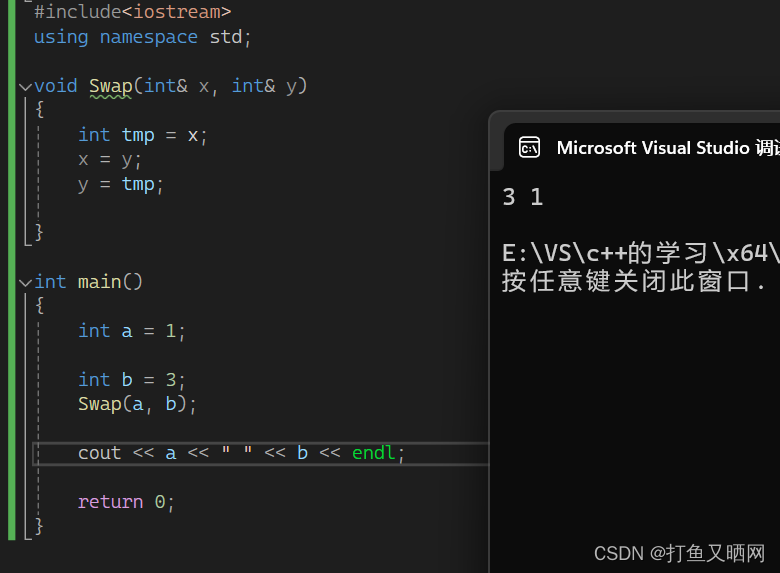

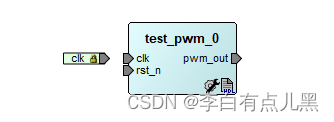

第一步,假设已经建立了两个文件,现在需要将这两个文件连接在一起,如下图所示:

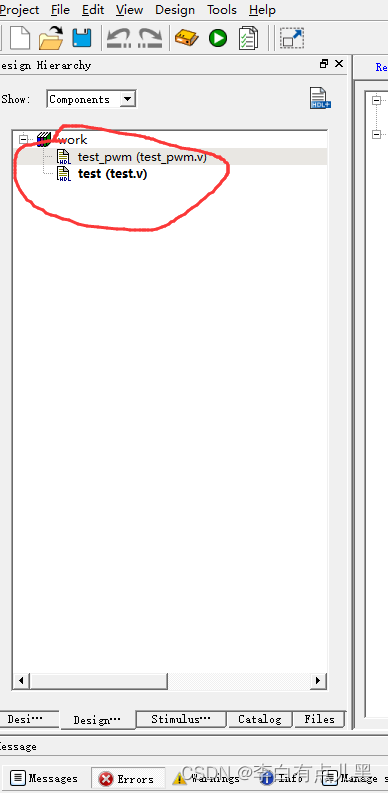

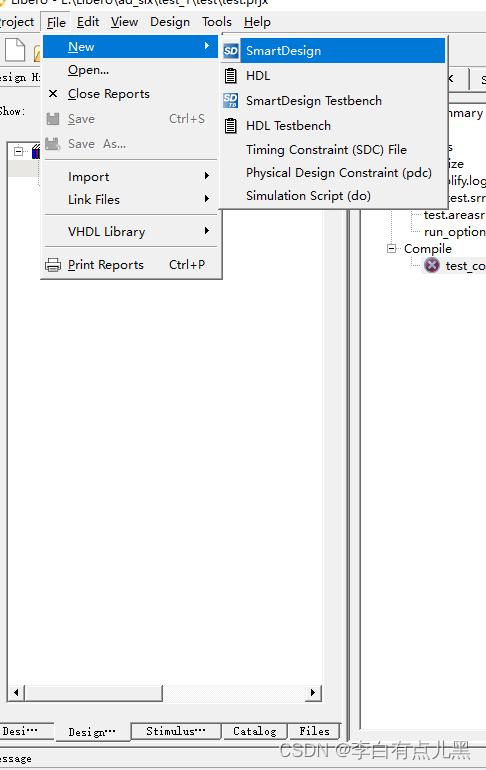

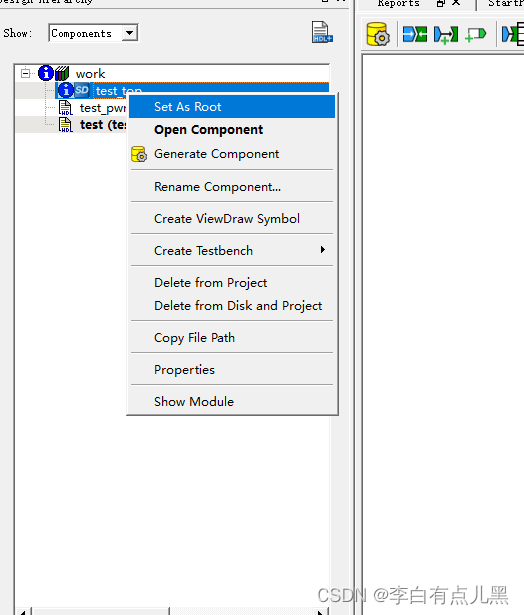

第二步,建立一个SD顶层文件,操作如下:

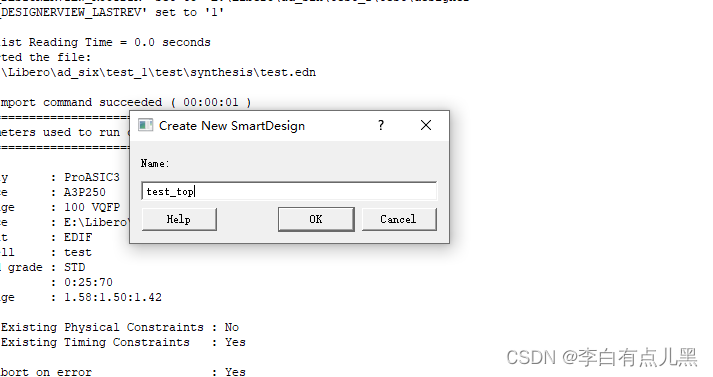

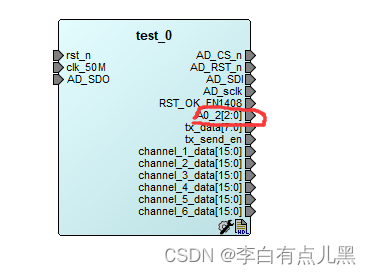

得到结果如下:

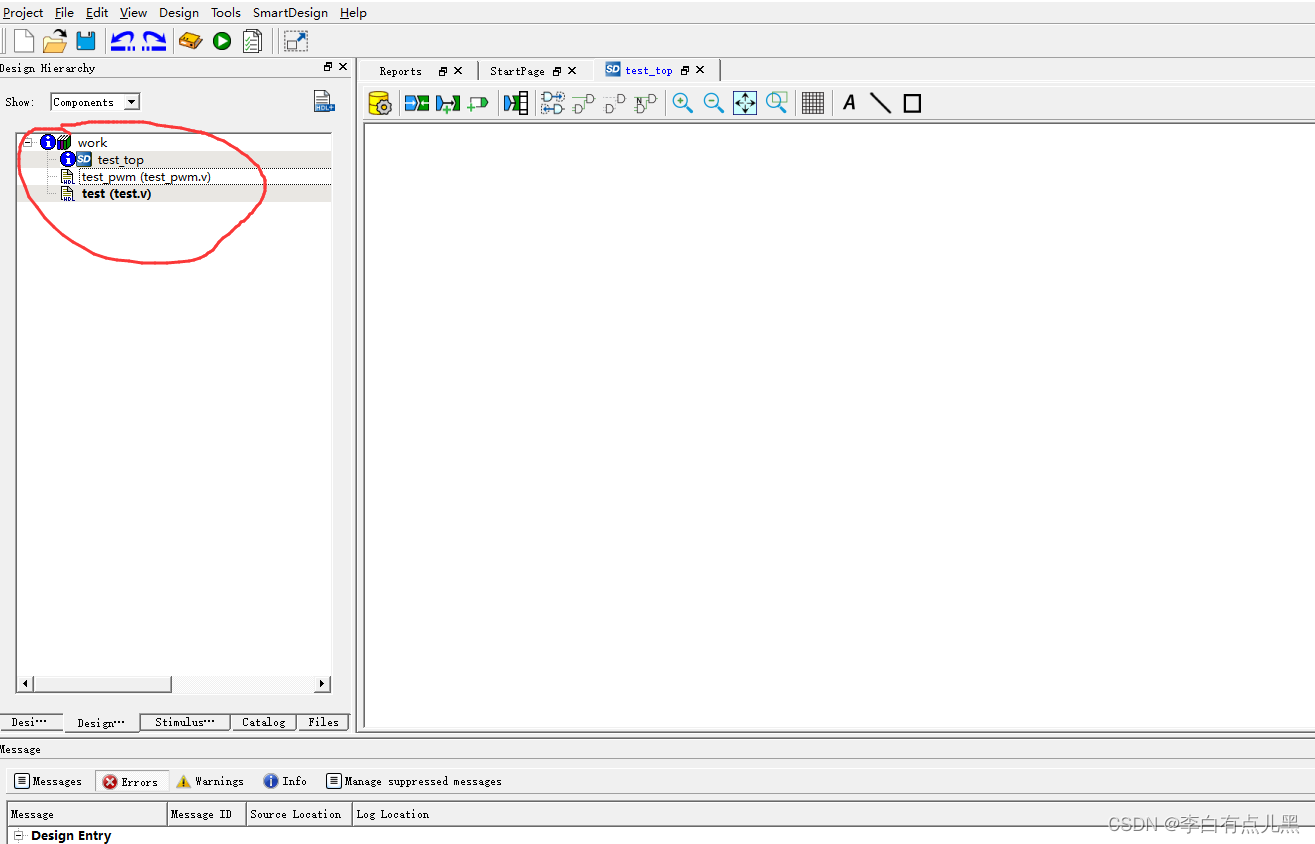

点击OK得到如下图所示:

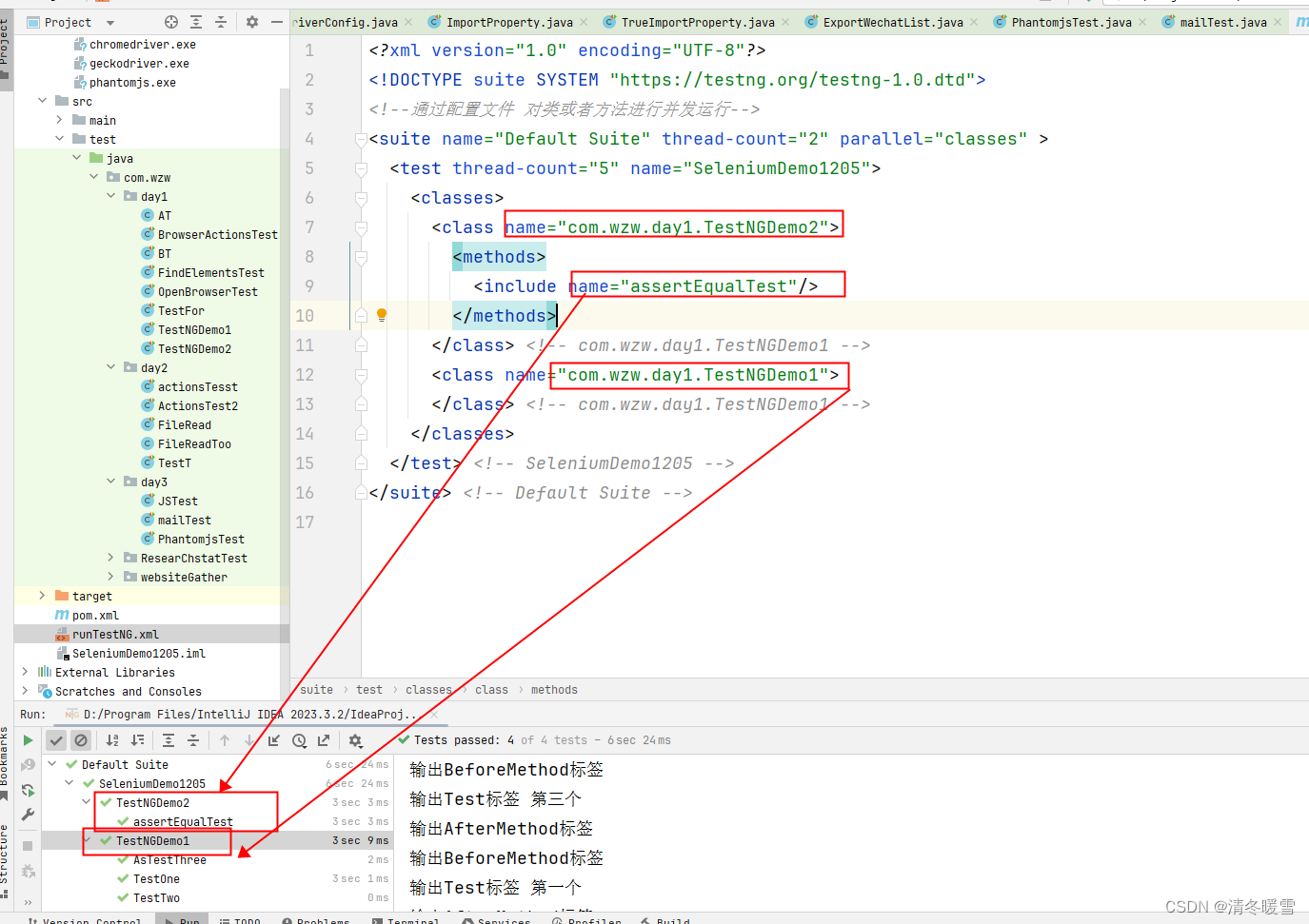

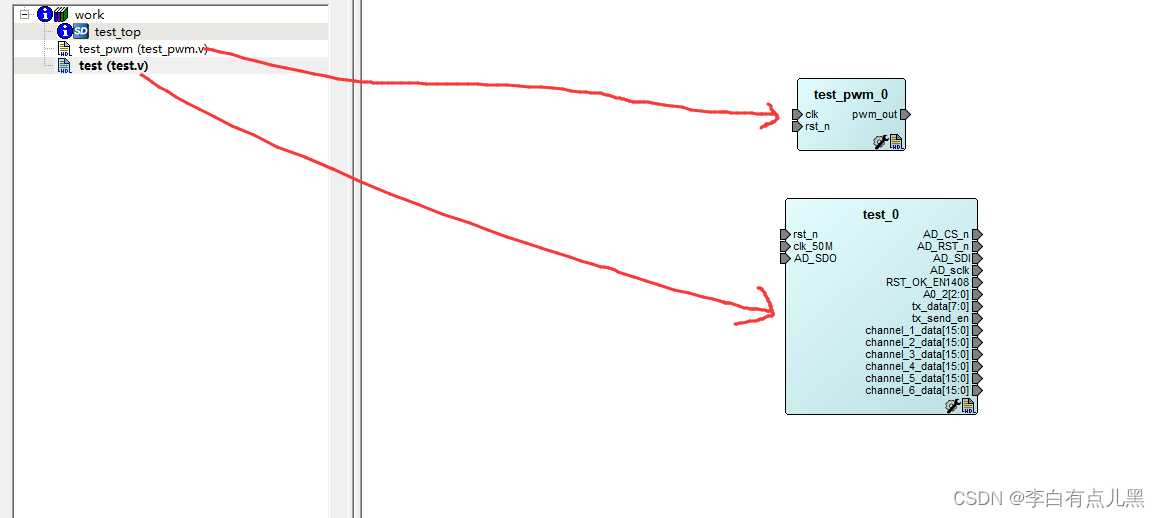

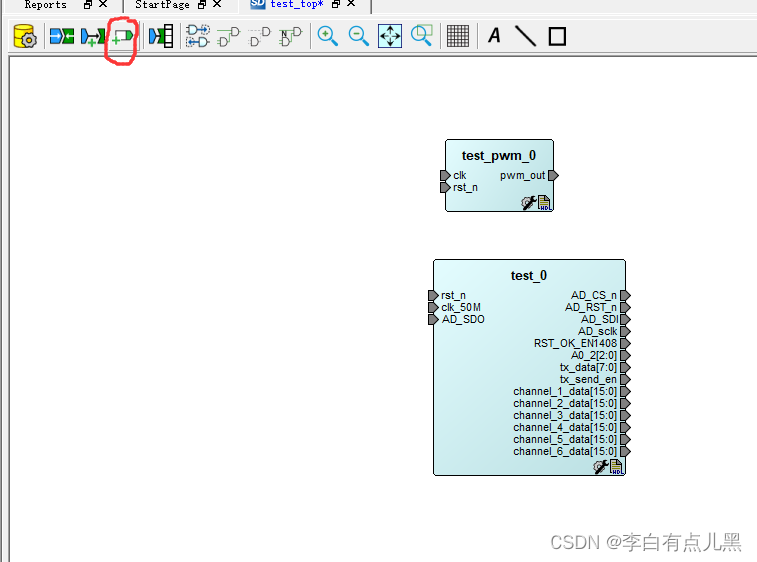

第三步:点击SD文件,然后把需要实例化的文件往SD文件空白处里拖即可,像下面这样:

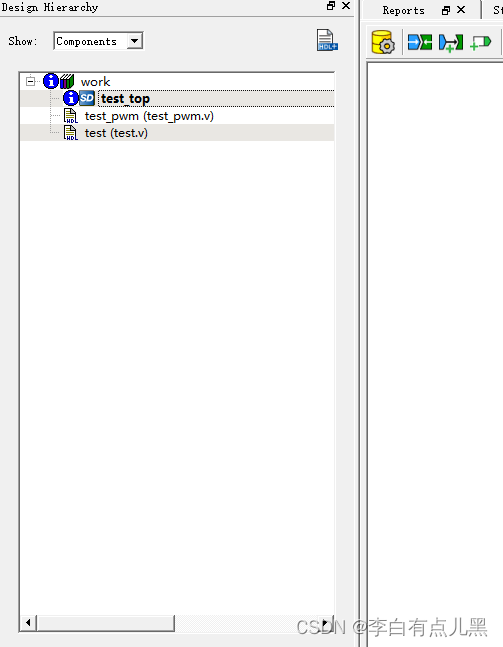

第四步:将SD文件设置为顶层文件

变成如下图所示:

第五步:结构已经搭好,下面开始连线

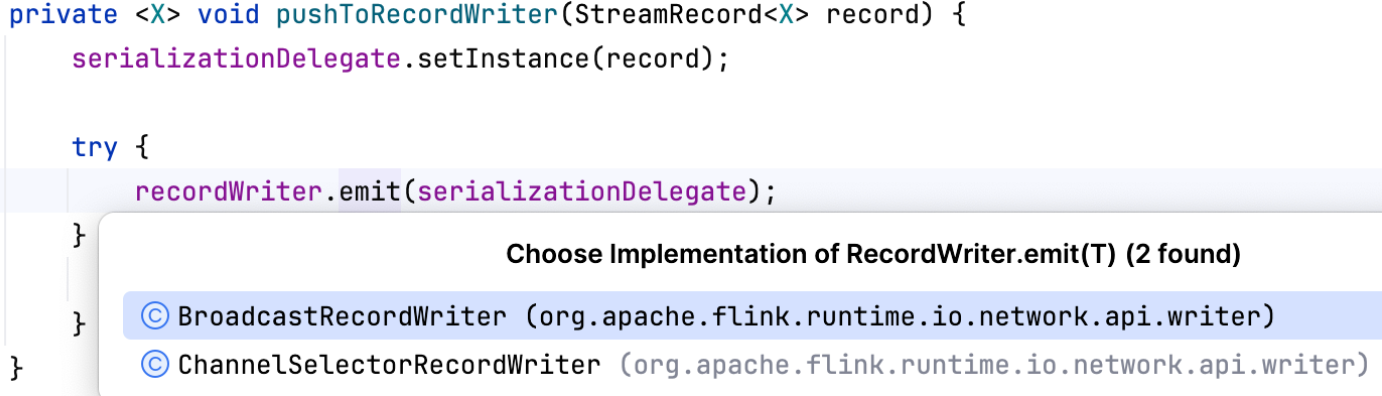

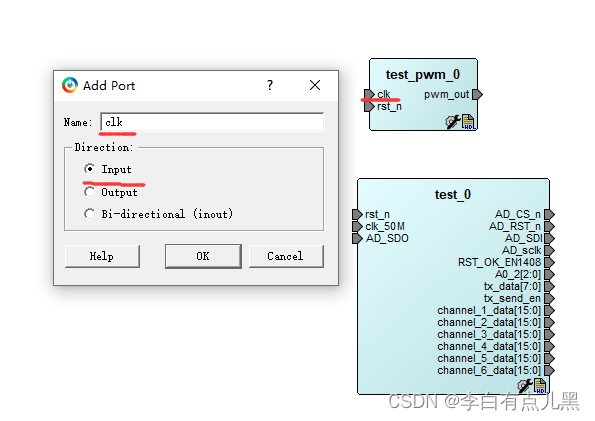

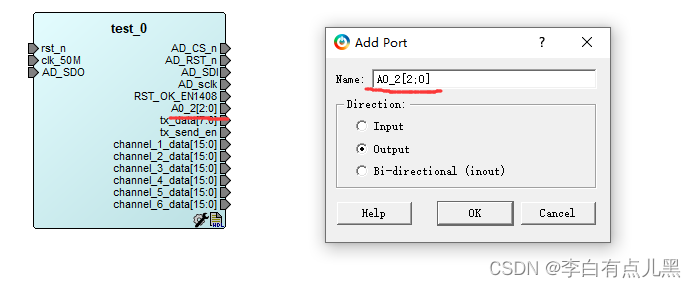

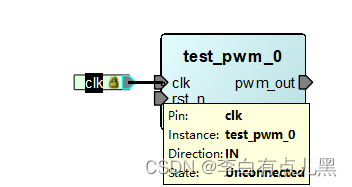

点击这个地方,给输入输出引脚起好名字,建议就和模块引脚名一致,如下面输入引脚 clk

点击OK即可

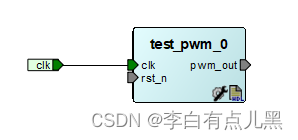

把他拖到clk附近,别的引脚操作一致,下面有个比较特殊的引脚:(没有这种引脚的可跳过)

这种一次性3个通道的如何配呢,就把它的名称敲出来即可,如下图所示:

注意:得是英文环境下的中括号

下面开始连线

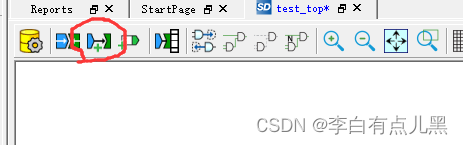

点击这个

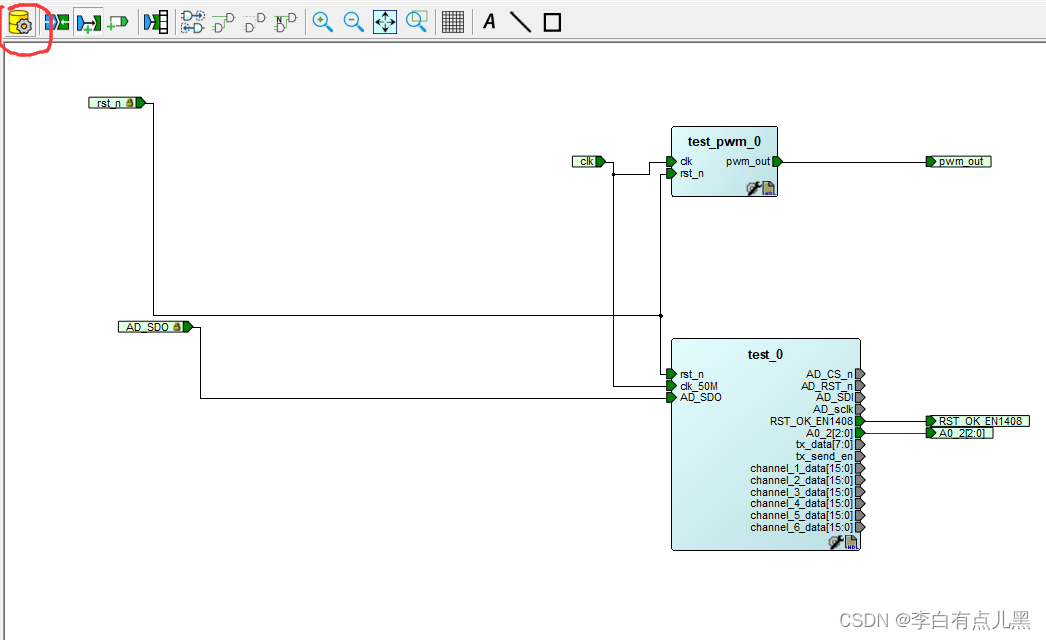

下面看一下全部连好的效果:

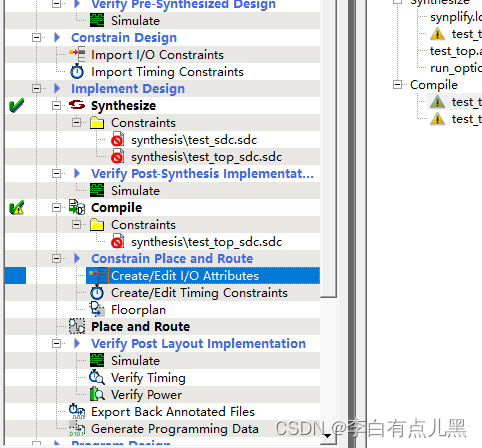

连接完之后点击这个编译没有报错即成功(不需要的输出引脚可以不接,但是输入引脚必须都得接),然后点击下图所示选项,可以成功进入IO口配置界面,即可表明工程没有问题。

最后请各位仁兄多多打赏多多关注,一起冲破Libero使用的技术封锁,大家一起加油。我是只发布高质量文章的李白有点儿黑