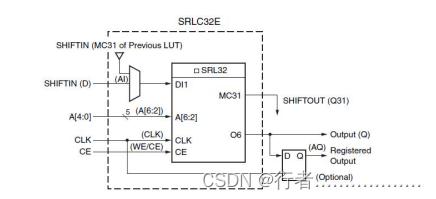

SLICEM中的LUT可以配置为32位移位寄存器,而无需使用slice中可用的触发器。以这种方式使用,每个LUT 可以将串 行数据延迟 1 到 32 个时钟周期。移入D (DI1 LUT 引脚)和移出 Q31(MC31 LUT 引脚)线路将LUT级联,以形成更大的移位寄存器。因此,SLICEM 中的四个 LUT 被级联以产生高达 128 个时钟周期的延迟。32 位移位寄存器调用原语:

SRLC32E #(.INIT(32h00000000))//移位寄存器的初始值

SRLC32E_inst (

.Q (Q), // SRL数据输出

.Q31(Q31), // SRL级联输出引脚。

.A(A), // 5位移位深度选择输入

.CE(CE), //时钟使能输入。

.CLK(CLK), //时钟输入。

.D (D)// SRL数据输入)。

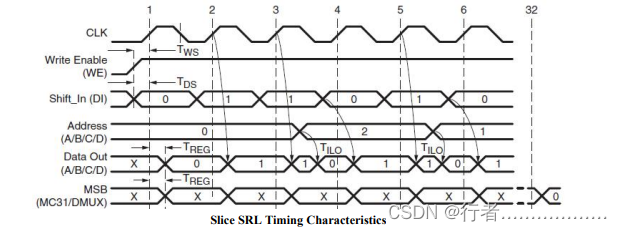

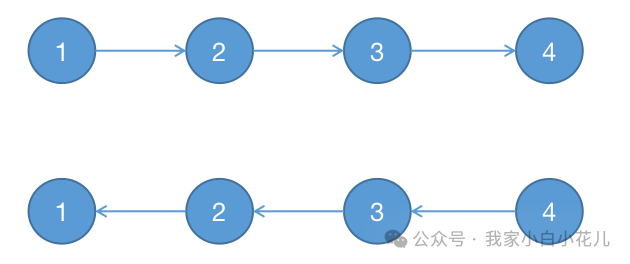

下图为其时序特性

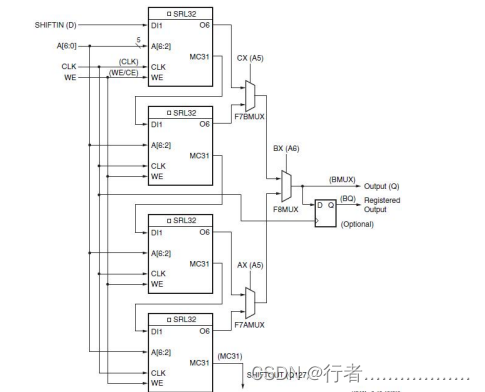

下图为级联的128移位寄存器

![基于JavaWeb开发的小区车辆登记系统计算机毕设[附源码]](https://img-blog.csdnimg.cn/direct/dd74cb8545a14f0daa0b2fcaba7be34e.png)

![基于JavaWeb开发的羽毛球管理系统计算机毕业设计[附源码]](https://img-blog.csdnimg.cn/direct/ccca37839aed4abb966e8d55f678dc4e.png)