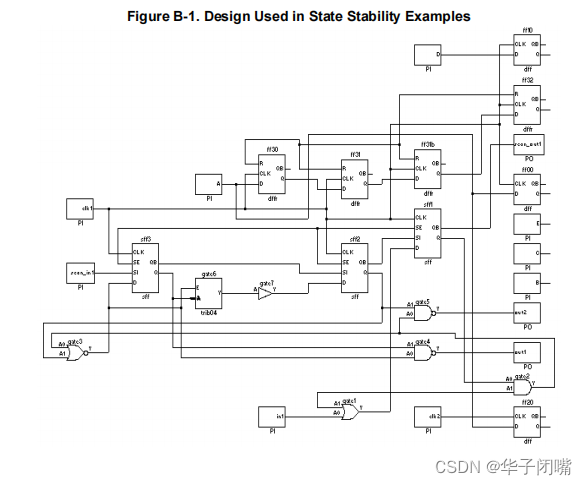

add_clocks 0 clk1 clk2 reset

add_scan_groups grp1 scan1.testproc

add_scan_chains c0 grp1 scan_in1 scan_out1

add_input_constraints D -c0

set_gate_report drc_pattern state_stability

set_system_mode analysis

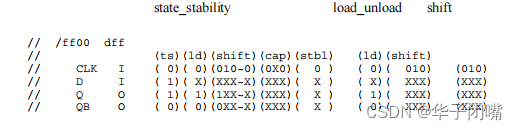

report_gates A B C D E

此操作的结果是:

•在test_setup中显式强制引脚A到E。

•引脚A、B、C和E强制加载卸载。

•引脚D受到约束(但在load_unload中不强制),是捕获期间唯一具有显式值的引脚。

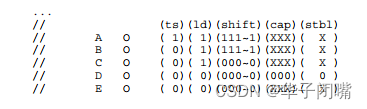

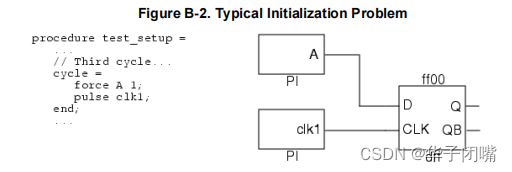

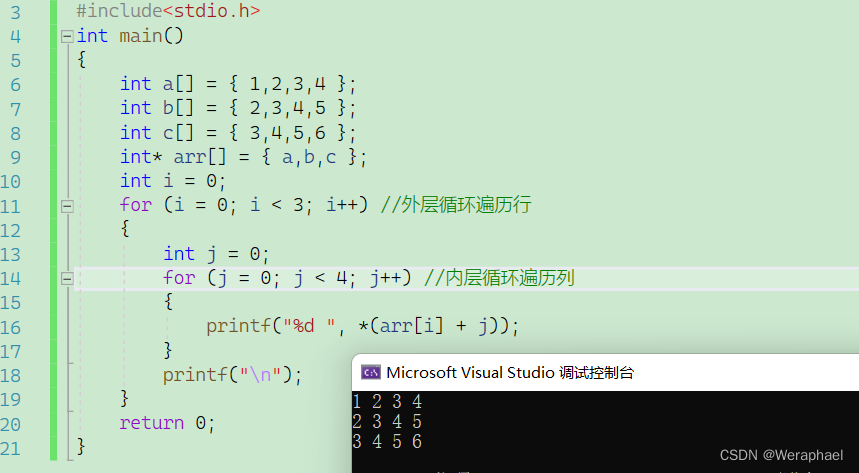

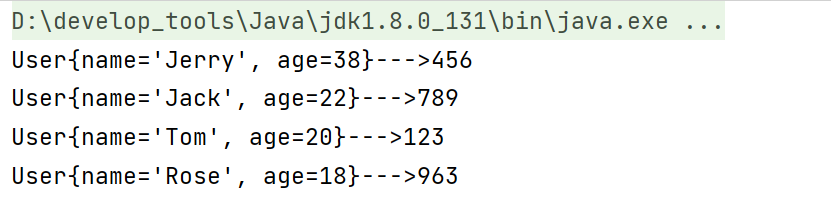

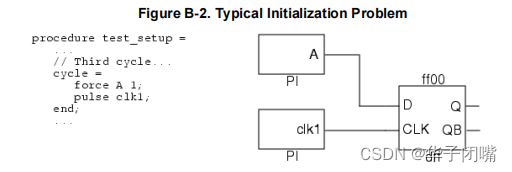

ff00中说明了一个典型的初始化问题。图B-2显示了test_setup过程中似乎初始化此触发器的相关电路和语句。

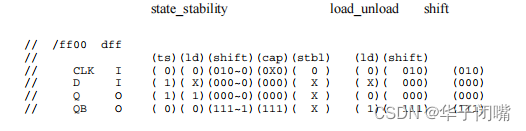

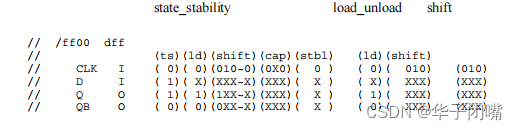

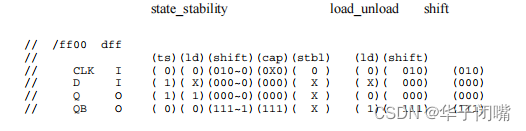

在这种情况下,您可能希望在初始化后输出始终为1,因为test_setup过程的第三个周期强制输入a和脉冲clk1为1。为了进行比较,以下是报告的state_stability数据以及为load_unload和shift报告的数据。特别注意Q输出:

从状态稳定性显示中可以看到,在test_setup之后,Q的输出设置为1。在load_unload的第一个应用程序中,它仍然是1,但在第一个shift中它变为X。将其与显示的“drc_pattern load_unload”和“drc_pattern shift”进行比较。

通过对ff00执行类似于ff10的操作,可以更好地实现稳定的初始化值,其中D输入连接到受约束的D引脚:

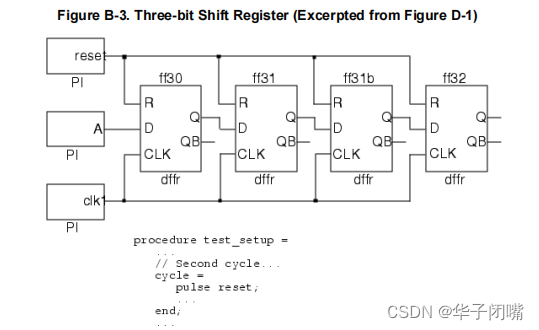

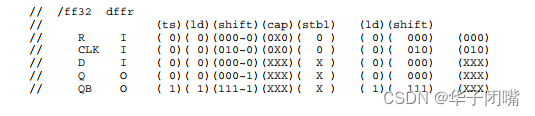

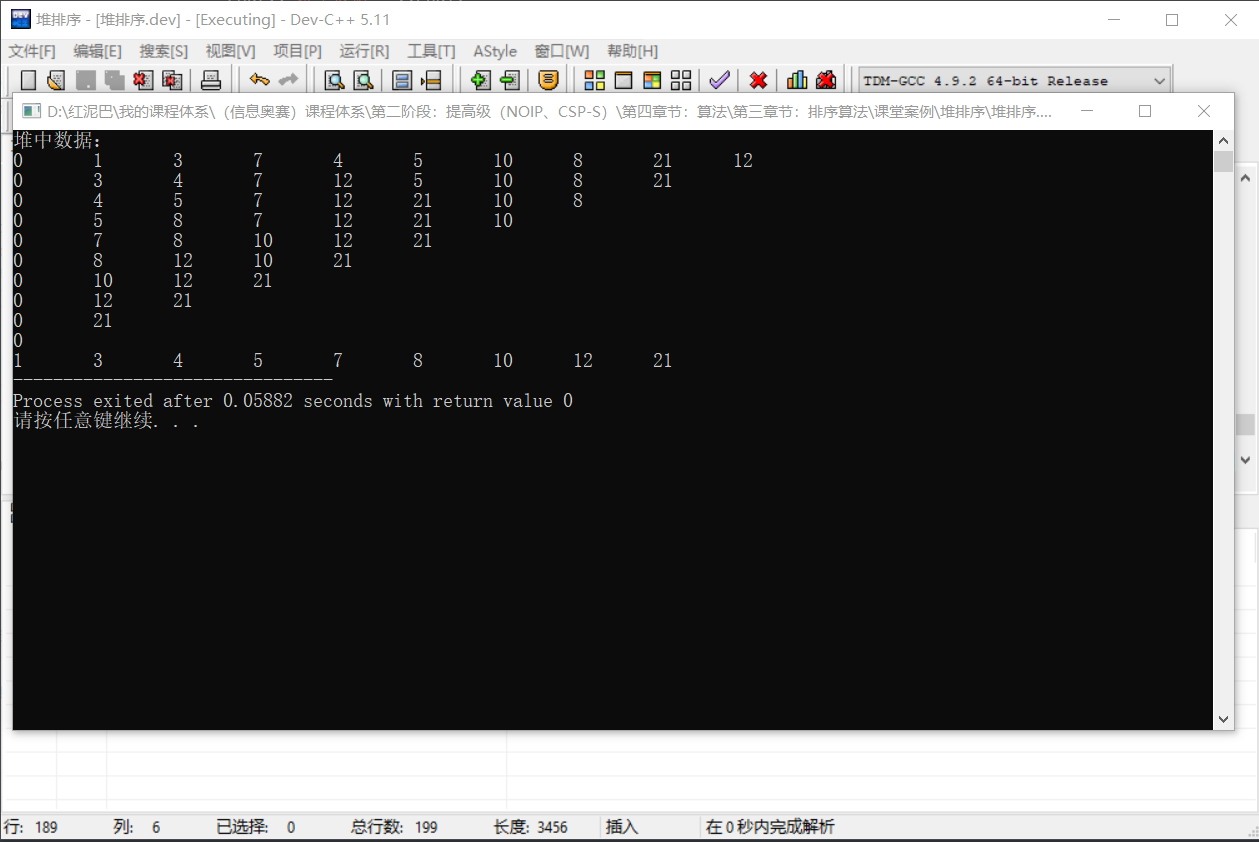

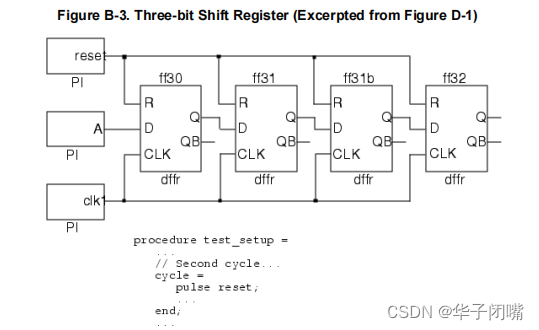

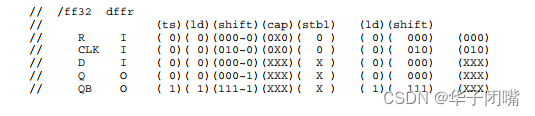

另一个有趣的观察结果是ff32。该触发器位于4位移位寄存器的末尾,在测试设置期间,所有触发器都被重置,如图B-3所示。

注意,在这种情况下,对于load_unload和shift的第一个应用程序,Q是稳定的,但是在最后一次shift(~之后)之后的稳定状态是X。(将此输出与示例9-将稳定性检查设置为Off和All_shift进行比较。)

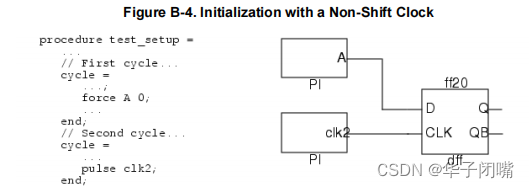

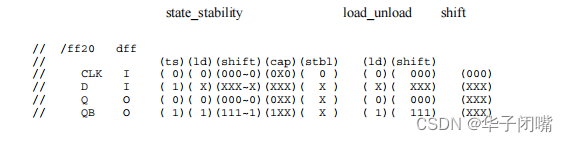

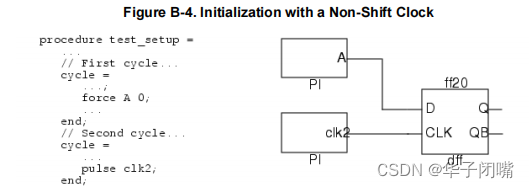

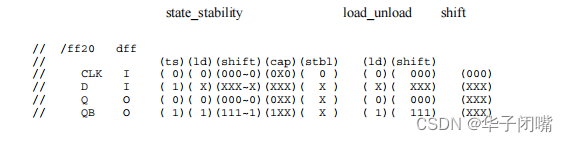

非扫描触发器ff20由不是移位时钟的clk2计时。如图B-4所示,该触发器也在test_setup期间初始化。

Q输出在捕获过程中受到干扰,而不是在移位过程中,因为移位过程中未执行此元素:

请注意,ff32和ff20的load_unload和shift数据几乎相同(除了时钟数据),但state_stability数据使您可以看到它们以非常不同的方式变得不稳定。

Example 2 — Multiple Cycles in Load_unload Prior

to Shift

本示例与基本示例之间的主要区别在于,在load_unload过程中,applyshift语句之前有多个循环(本示例中的新语句以粗体突出显示)。

procedure load_unload =

scan_group grp1 ;

timeplate gen_tp1 ;

// First cycle, one PI event (force)

cycle =

force clk1 0 ;

force clk2 0 ;

force reset 0 ;

force scan_en 1 ;

force B 1;

force C 1;

force E 1;

end ;

// Second cycle, three PI events

(force, pulse on, pulse off)

cycle =

force E 0;

pulse clk2;

end ;

// Third cycle, two PI events

(pulse on, pulse off)

cycle =

pulse clk2;

end ;

apply shift 3;

end;

作为结果,在第二组状态稳定性数据中显示多个事件。注意现在有三个循环。以下gate报告摘录显示了六位数据,与事件总数相对应。第一个比特来自第一个周期(一个事件),接下来的三个比特来自第二个周期(三个事件)。最后两个比特来自具有两个事件的第三个周期。

// /E primary_input

// (ts)( ld )(shift)(cap)(stbl)

// E O ( 0)(

100000

)(000~0)(XXX)( X)

// /A primary_input

// (ts)( ld )(shift)(cap)(stbl)

// A O ( 1)(

XXXXXX

)(XXX~X)(XXX)( X)

// /clk2 primary_input

// (ts)( ld )(shift)(cap)(stbl)

// clk2 O ( 0)(

001010

)(000~0)(0X0)( 0)

// /ff20 dff

// (ts)( ld )(shift)(cap)(stbl)

// CLK I ( 0)(

001010

)(000~0)(0X0)( 0)

// D I ( 1)(

XXXXXX

)(XXX~X)(XXX)( X)

// Q O ( 0)(

00XXXX

)(XXX~X)(XXX)( X)

// QB O ( 1)(

11XXXX

)(XXX~X)(XXX)( X)

请注意,对于load_unload模拟,A是如何转到X的。这是因为它没有在load_unload过程中显式强制(或使用add_input_constrats命令约束)。

Example 3 — Drc_pattern Reporting for Pulse

Generators

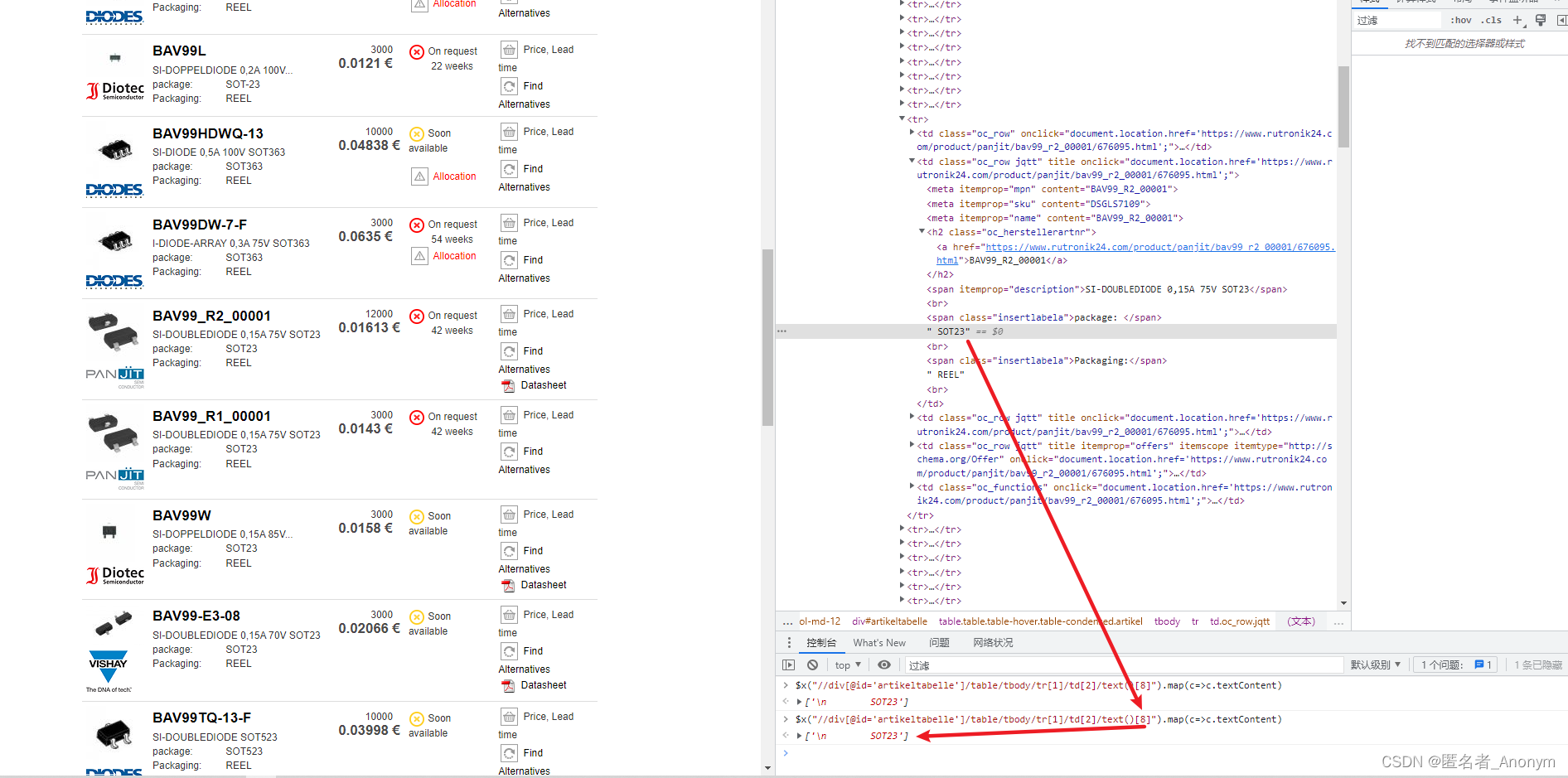

如果电路包含具有用户定义定时的脉冲发生器(PG),该工具将对PG的输出变化执行额外的模拟步骤。当上升沿事件发生在其输入端时,PG在一定延迟后输出1,工具将其模拟为附加事件。

在另一个延迟之后,PG的输出信号返回到0,这也被模拟为一个单独的事件。两个输出事件都添加到输入事件后面的一对括号([])内的报告中。假设前面示例的非扫描触发器ff20由PG计时,如图B-5所示。下图摘录显示了PG事件如何出现在gate报告中。

// /clk2 primary_input

// (ts)( ld )(shift)( cap )(stbl)

// clk2 O ( 0)(00

1

[11]0

1

[11]0)(000~0)(0X[X]0)( 0) /pg1/clk

// /pg1 pulse_gen

// (ts)( ld )(shift)( cap )(stbl)

// clk I ( 0)(00

1

[11]0

1

[11]0)(000~0)(0X[X]0)( 0) /clk2

// out O ( 0)(000[

10

]00[

10

]0)(000~0)(00[X]0)( 0) /ff20/CLK

// /ff20 dff

// (ts)( ld )(shift)( cap )(stbl)

// CLK I ( 0)(000[10]00[10]0)(000~0)(00[X]0)( 0) /pg1/out

// D I ( 1)(XXX[XX]XX[XX]X)(XXX~X)(XX[X]X)( X) /A

// Q O ( 0)(000[XX]XX[XX]X)(XXX~X)(XX[X]X)( X)

// QB O ( 1)(111[XX]XX[XX]X)(XXX~X)(XX[X]X)( X)

clk2上的上升沿事件启动pg1的两个输出脉冲(以粗体突出显示)。请注意,脉冲不会与引起它们的输入变化同时显示。这是与输入变化同时出现的输出变化的典型显示的例外,如ff20所示。还请注意,ff20的CLK输入处的活动时钟边沿比clk2的活动边沿晚一个事件,并且由于括号的原因,被视为PG信号。

Example 4 — Single Post Shift

此示例在load_unload过程中有多个循环。新增的是single post shift

procedure load_unload =

scan_group grp1 ;

timeplate gen_tp1 ;

// First cycle, one PI event (force)

cycle =

force clk1 0 ;

force clk2 0 ;

force reset 0 ;

force scan_en 1 ;

force B 1;

force C 1;

end ;

// Second cycle, three PI events (force, pulse on, pulse off)

cycle =

force E 0;

pulse clk2;

end;

apply shift 2;

apply shift 1;

end;

在这种情况下,状态稳定性数据在主移位和捕获周期之间有一个附加组(以粗体显示)。这对应于后移的第一次应用:

// /ff32 dffr

// (ts)( ld )(shift)

(shift)

(cap)(stbl)

// R I ( 0)(0000)(000~0)

( 000)

(0X0)( 0) /reset

// CLK I ( 0)(0000)(010~0)

(010 )

(0X0)( 0) /clk1

// D I ( 0)(0000)(000~X)

( XXX)

(XXX)( X) /ff31b/Q

// Q O ( 0)(0000)(000~X)

( XXX)

(XXX)( X)

// QB O ( 1)(1111)(111~X)

( XXX)

(XXX)( X)

你可以看到ff32在第一次应用shift时非常稳定。如果在这种情况下使用set_stability_check All_shift命令,则输出略有不同:

set_stability_check all_shift

set_system_mode setup

set_system_mode analysis

report_gates ff32

// /ff32 dffr

// (ts)( ld )(shift)

(shift)

(cap)(stbl)

// R I ( 0)(0000)(000~0)

( 000)

(0X0)( 0) /reset

// CLK I ( 0)(0000)(010~0)

(010 )

(0X0)( 0) /clk1

// D I ( 0)(0000)(000~1)

( 1XX)

(XXX)( X) /ff31b/Q

// Q O ( 0)(0000)(000~0)

( 011)

(1XX)( X)

// QB O ( 1)(1111)(111~1)

( 100)

(0XX)( X)

请注意,ff32在整个主移位应用程序中现在是0,但在后移位期间设置为1。这是由于在test_setup中将A设置为1,并且该脉冲计时通过。