实现DDS通常有两种方式,一种是读取ROM存放的正弦/余弦信号的查表法,另一种是用DDS IP核。这篇学习笔记中,我们要讲解说明的是VIVADO DDS IP核的应用。 目前本篇默认Phase Generator and SIN/COS LUT(DDS)的standard模式,至于其他模式,目前没有研究使用过,没有话语权,以后研究明白再来续写。

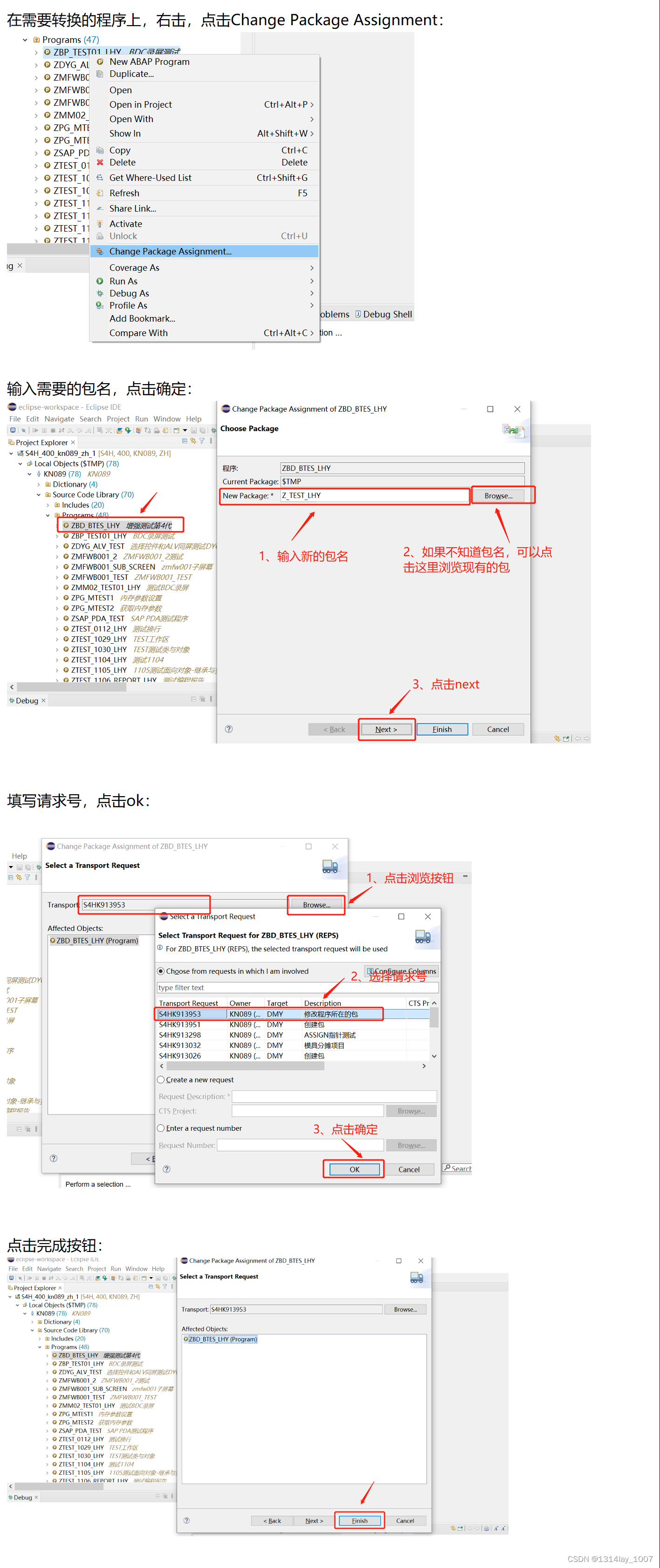

一、DDS IP配置

下面的配置说明都是本人参考技术手册加上自己的理解,可能会有误解的地方,追求原汁原味的知识点的话还是去看技术手册。

Configuration Tab

Configuration Options:

1.Phase Generator and SIN/COS LUT

2.Phase Generator only

从配置选项的名字就能够清晰的看出每种选项代表的功能,但是有必要注意的是 Phase Generator and SIN/COS LUT才是DDS。

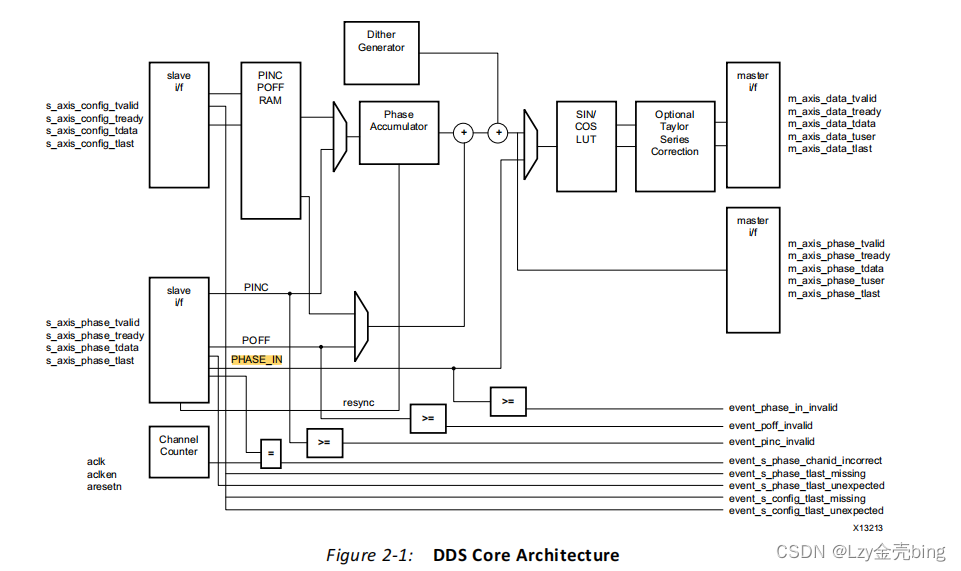

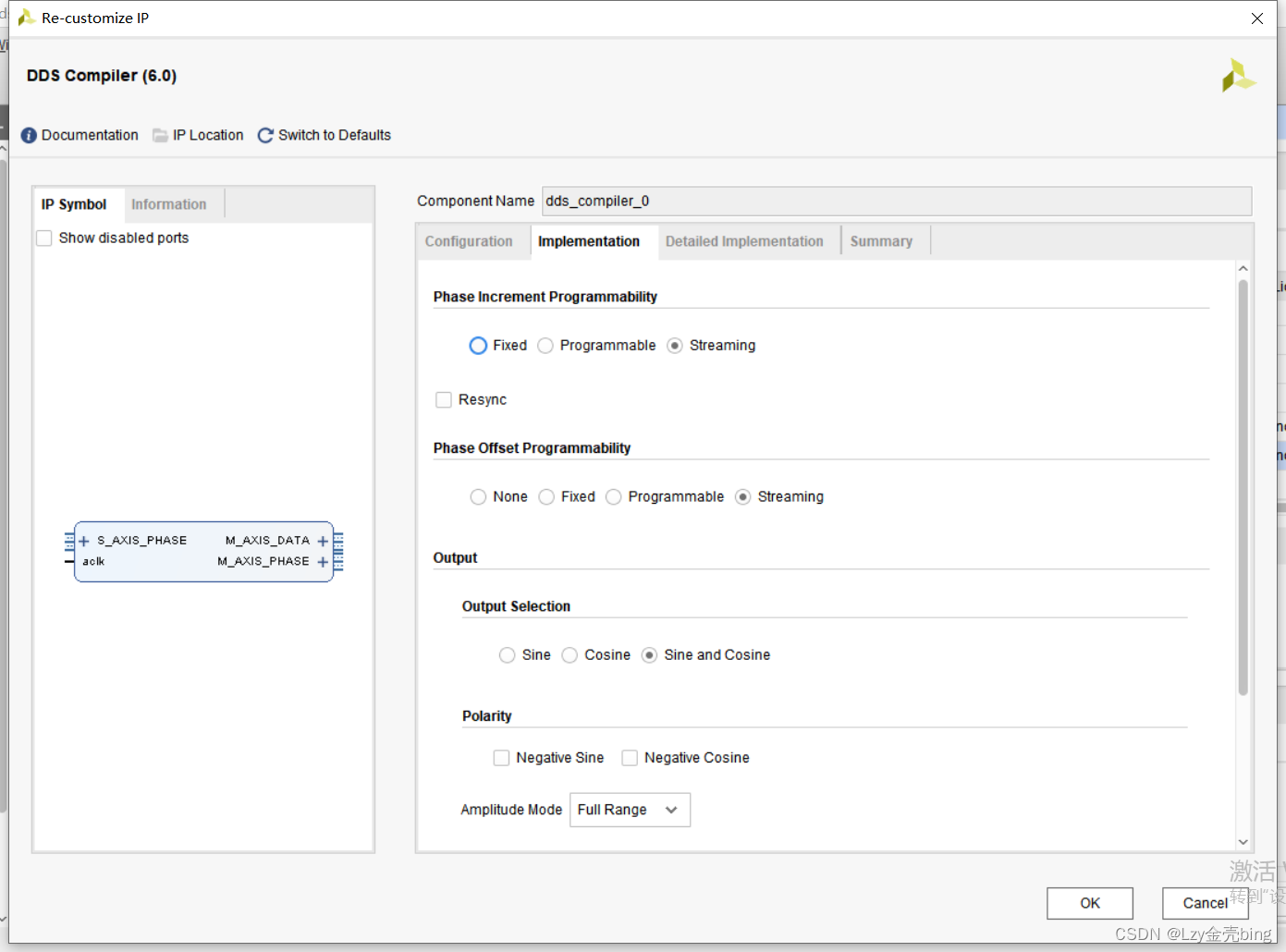

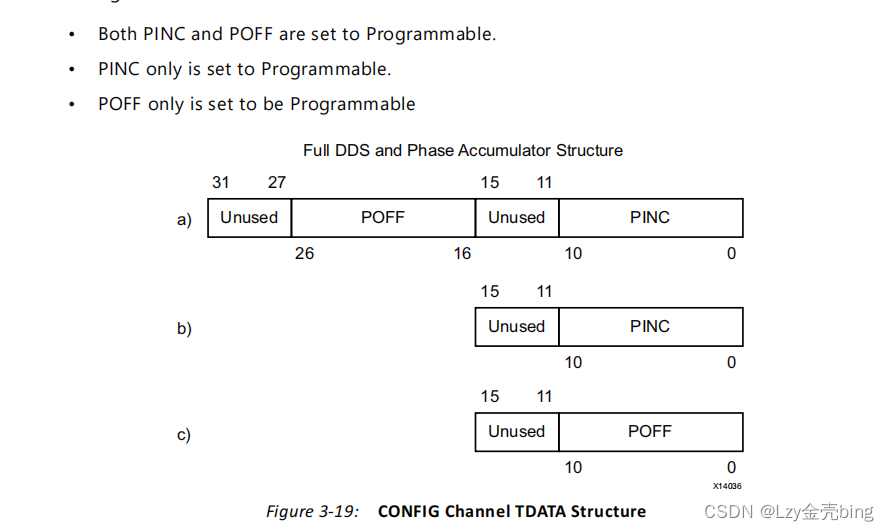

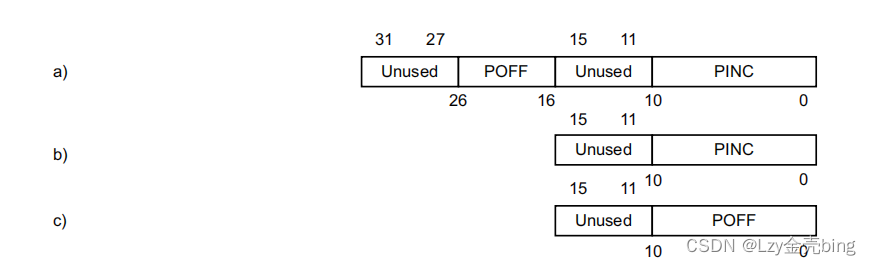

Phase Generator:如上图所示,Phase Generator由一个accumulator和一个可选的adder组成,以提供相位偏移的附加。在制定IP核时,相位增量(PINC)和相位偏移(POFF)可以被配置为fixed、programmable(用config 通道)或者streaming(用phase通道)三种模式。

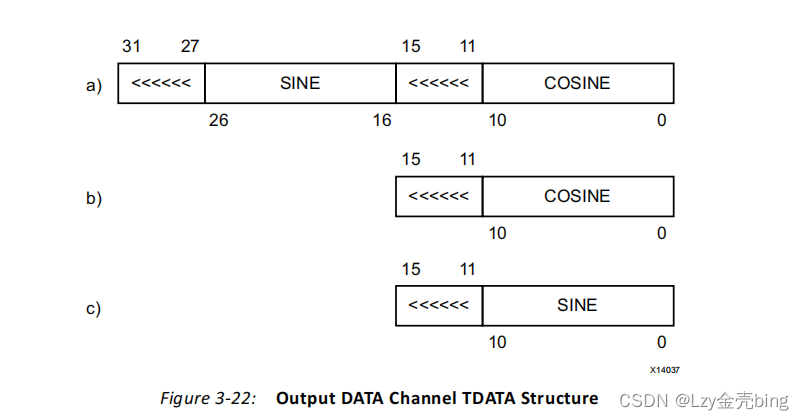

SIN/COS LUT:当仅配置为SIN/COS LUT,不生成Phase Generator时,PHASE_IN信号通过phase通道输入,并使用look-up table(LUT)转化为sine和cosine信号。IP核可以配置为仅sine输出,仅cosine输出或两者(正交)都输出,每个输出都可以独立配置为反向输出。可使用可选的Taylor series correction(泰勒级数校正)增加精度。

Phase Generator and SIN/COS LUT:Phase Generator与SIN/COS LUT一起使用可以组合成为phase truncated DDS(相位截位DDS)或Taylor series correction DDS(泰勒级数校正DDS),也可以在两个块之间添加一个可选的dither generator组合成phase dithered DDS(相位抖动DDS)。

System Clock:DDS核心的时钟频率。其实就是输出信号的采样率。

Number of Channels:最多支持16个通道,这些通道时间被复用,这降低了每个信道的有效时钟频率。开启多个通道相当于降低采样率。

Mode of Operation:有standard和rasterized两种模式选择。(目前默认讲解standard)

Frequency per Channel (Fs):由于分时复用,每个信道的有效时钟是System clock除以Number of Channels。

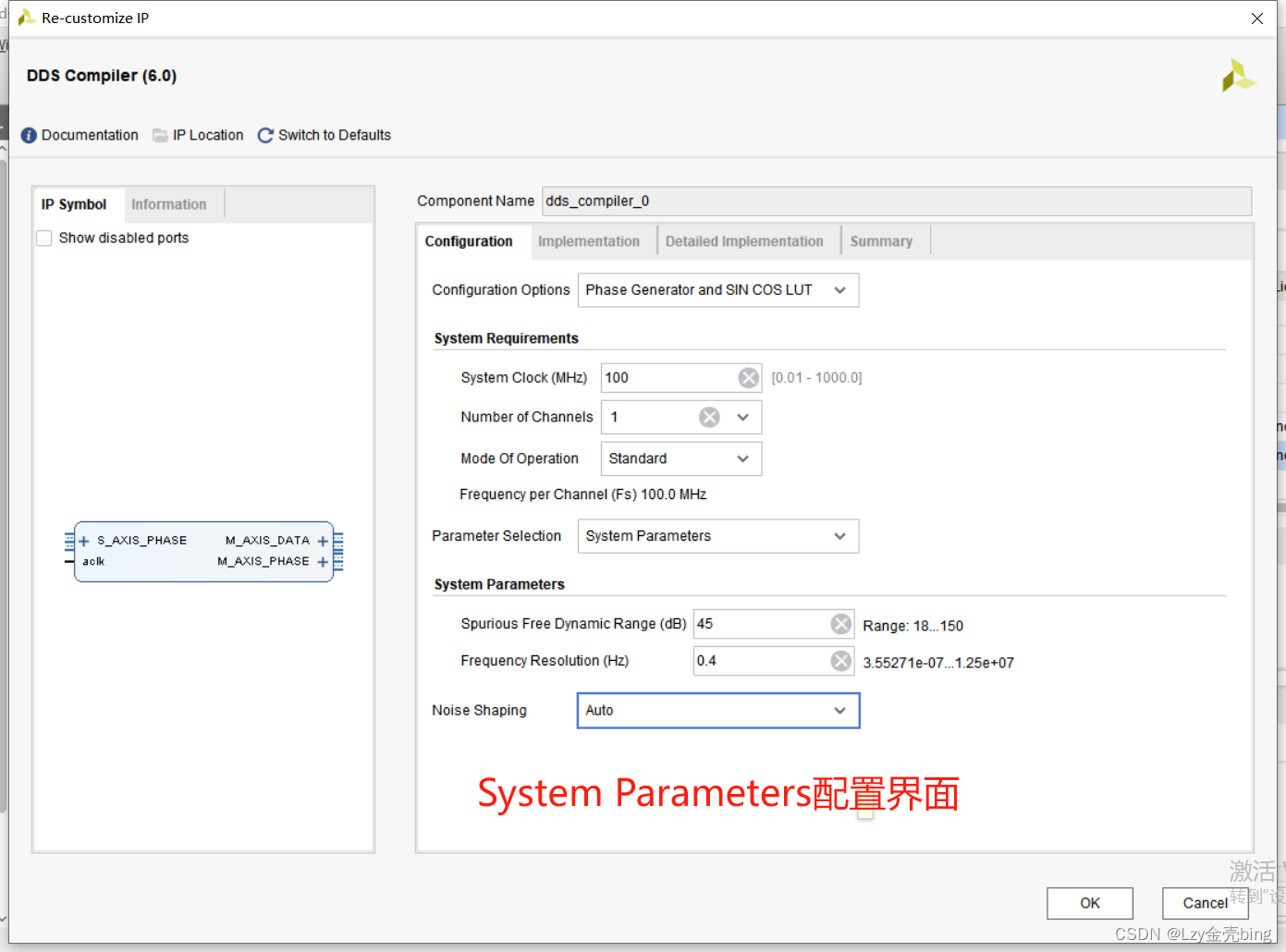

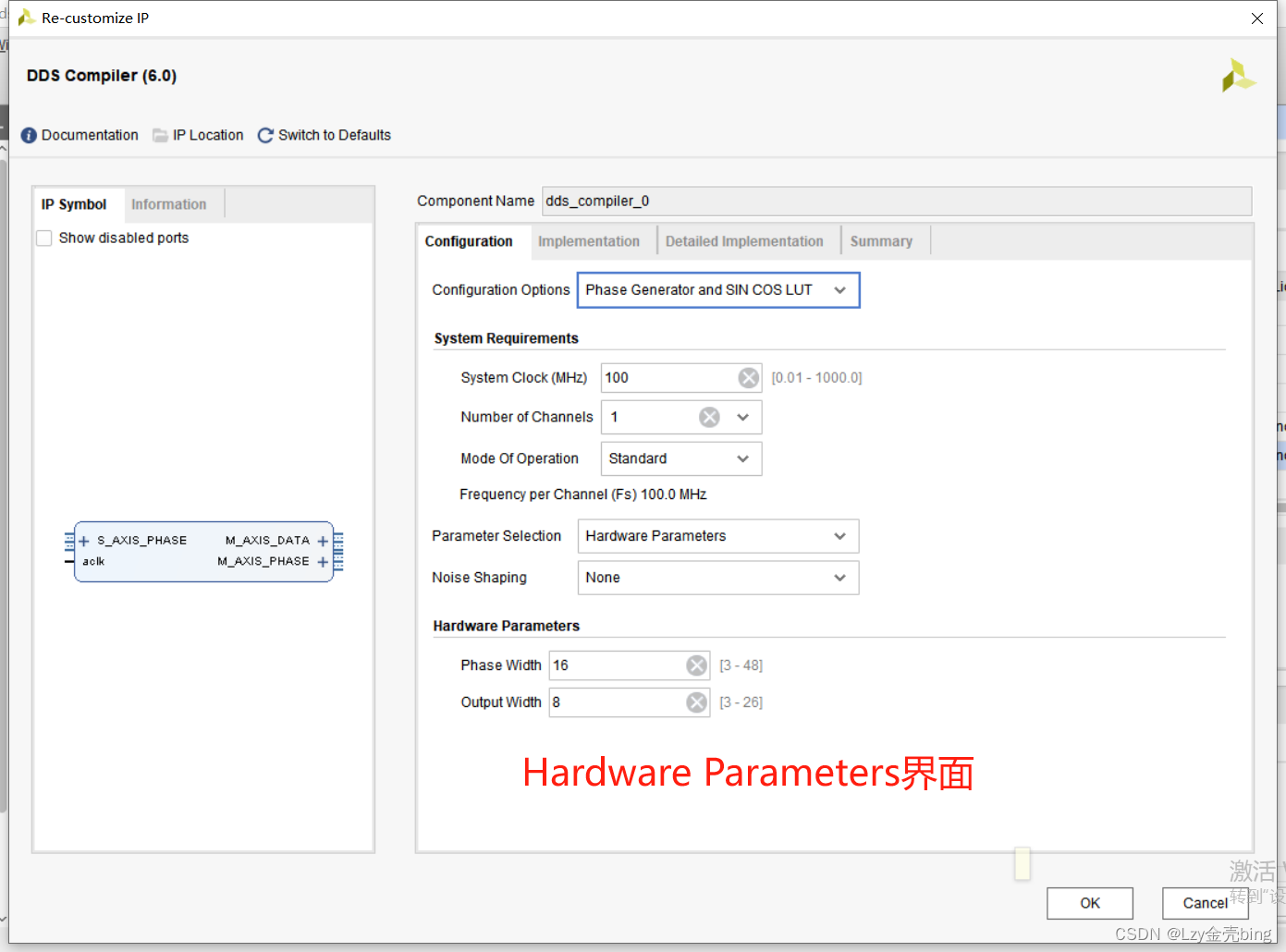

Parameter Selection:DDS关键参数可以使用System parameters来指定,这些参数针对系统架构师(频域参数),也可以使用Hardware parameters,主要针对硬件工程师(时域参数)。这个条件下

Phase Generator和SIN/COS LUT仅根据Hardware parameters指定。

System parameters:如上图System parameters界面,

1.Spurious Free Dynamic Range(SFDR):DDS产生信号的质量,用于设置输出宽度以及内部总线宽度和各种实现决策。

2.Frequency Resolution设置最小频率分辨率,并用于确定相phase accumulator及其相关的相位增量(PINC)和相位偏移(POFF)值所使用的相位宽度(Phase Width)。值越小,分辨率越高,需要更大的累加器。通过选择Noise Shaping可以使Phase Width增加,频率分辨率比指定的更高,

3.Noise Shaping控制是否使用相位截位(phase truncation)、抖动(dithering)或Taylor series correction(泰勒级数校正)。None:Phase truncation DDS。Dithering:相位抖动用于改善SFDR,但代价是增加本底噪声。Taylor Series Corrected:将相位截位中丢弃的bit对Sine/cosine进行插值。Auto:根据SFDR等System parameters自动确定Noise Shaping。

Hardware parameters:如上图Hardware parameters界面。

1.Phase Width:设置m_axis_phase_tdata中PHASE_OUT字段的宽度。

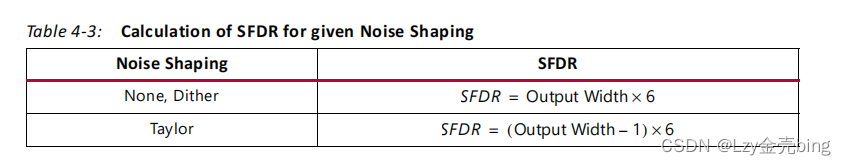

2.Output Width:只有在选择DDS或SIN/COS LUT部件时才启用,因为Phase

Generator不需要它,用来设置在m_axis_data_tdata中设置SINE和COSINE字段的宽

度。它提供的SFDR取决于Noise Shaping 的选项,计算方式如图:

Implementation Tab

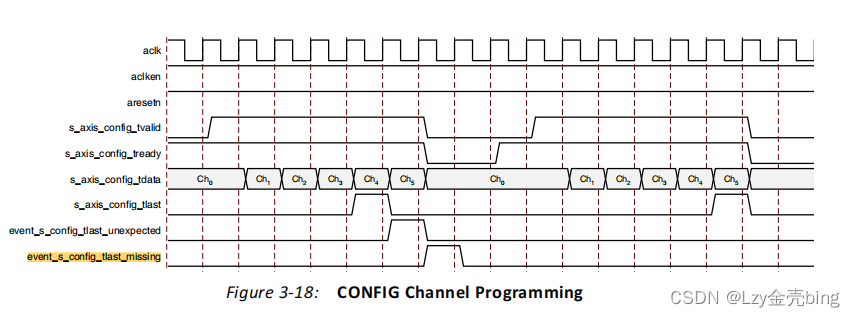

第二个编程周期显示了TLAST的正确应用。

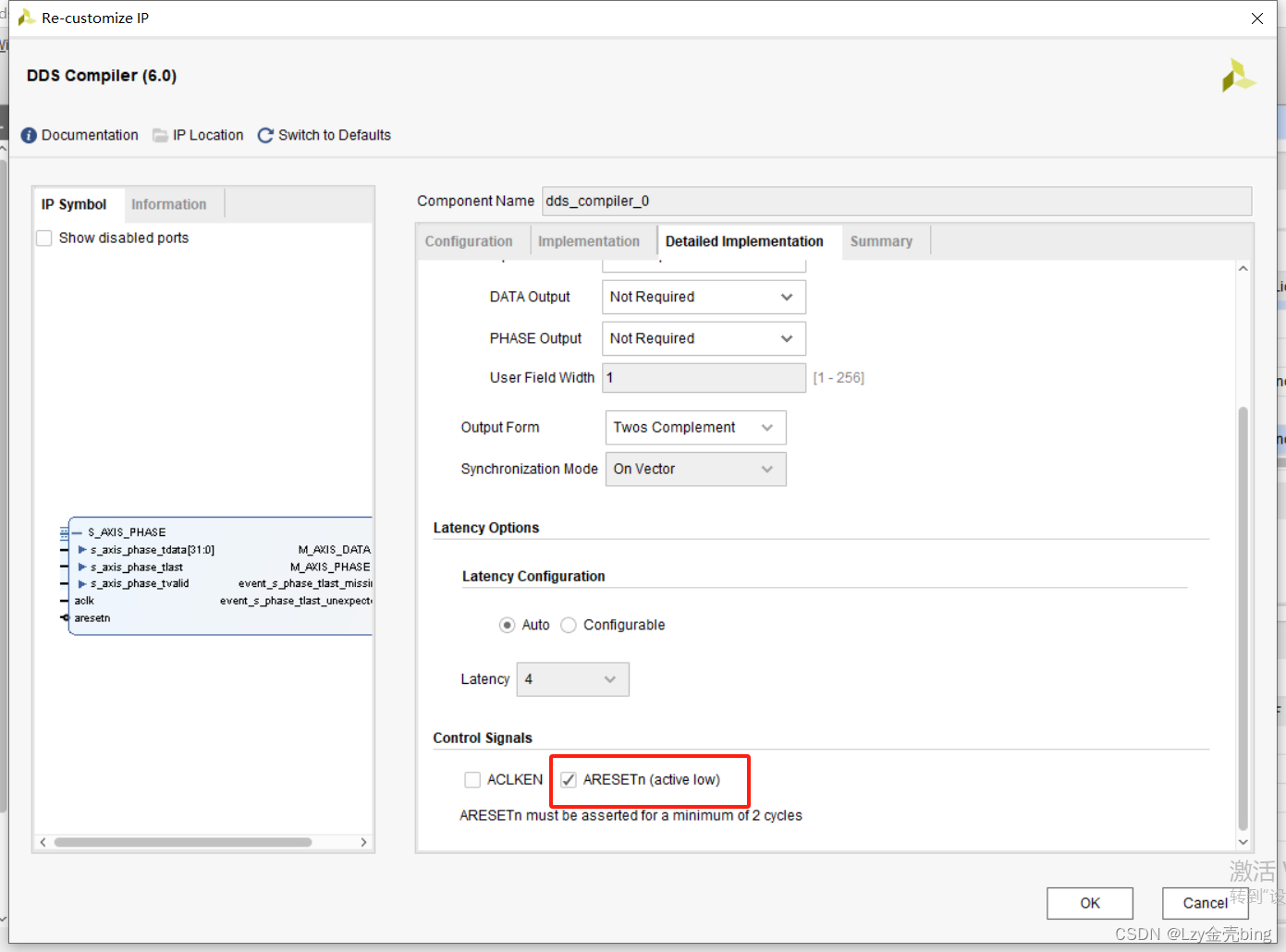

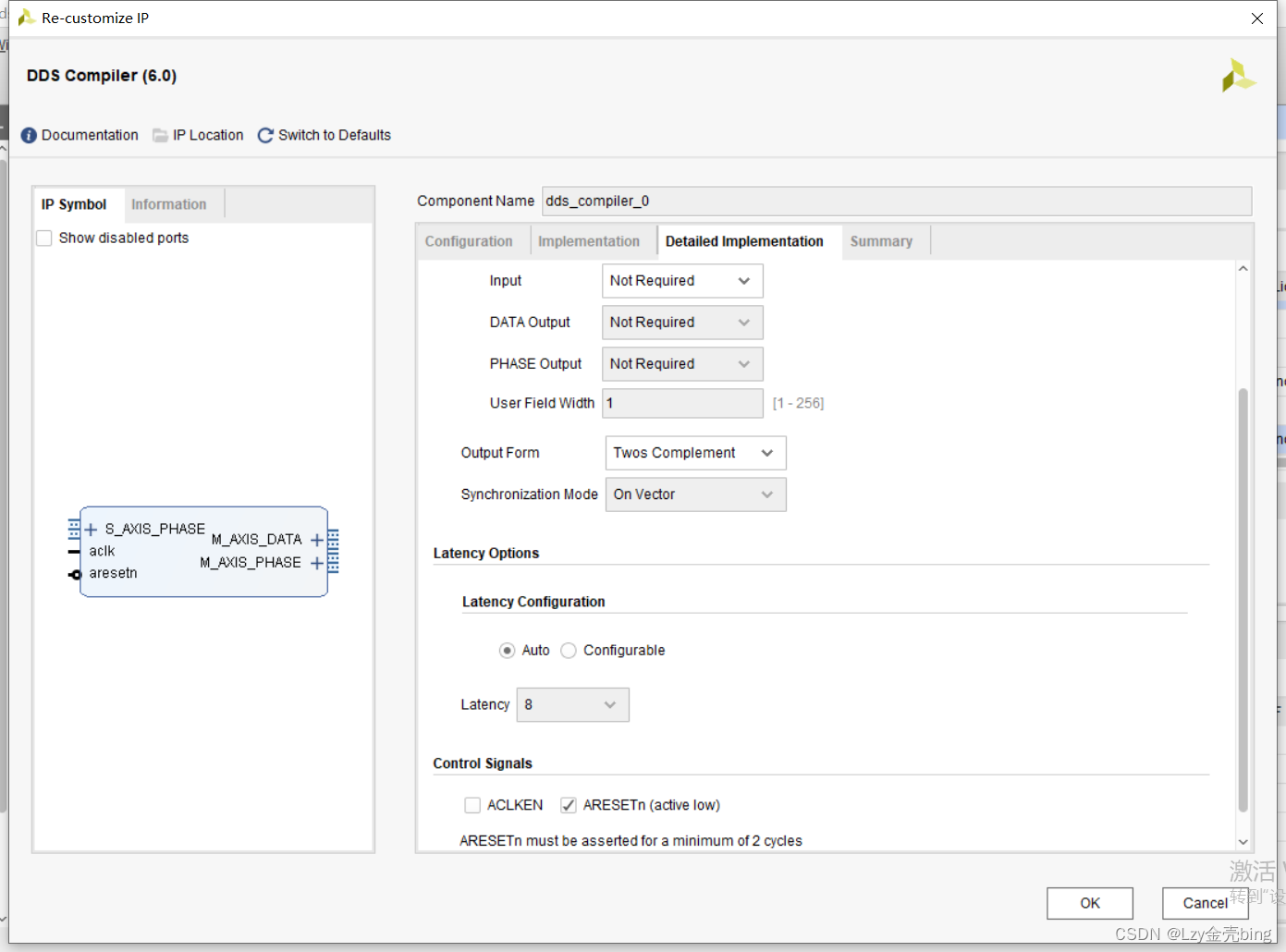

Detailed Implementation Tab

举例:

dds_compiler_0 your_instance_name (

.aclk(aclk), // input wire aclk

.aresetn(aresetn), // input wire aresetn

.s_axis_phase_tvalid(s_axis_phase_tvalid), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(s_axis_phase_tdata), // input wire [63 : 0] s_axis_phase_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata), // output wire [31 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata) // output wire [31 : 0] m_axis_phase_tdata

);

拓展延申

genvar i;

generate

for(i=0; i<channal; i=i+1)begin:channal_i

always @(posedge clk or posedge rst)begin

if(rst)begin

PINC[i] <= 'h0;

POFF[i] <= 'h0;

s_axis_phase_tvalid[i] <= 1'b0;

end

else begin

PINC[i] <= PINC_adjust;

POFF[i] <= (PINC_adjust/channal)*i;

s_axis_phase_tvalid[i] <= 1'b1;

end

end

dds_compiler_0 dds_compiler_0 (

.aclk(clk),

.aresetn(aresetn),

.s_axis_phase_tvalid(s_axis_phase_tvalid[i]),

.s_axis_phase_tdata({POFF[i],PINC[i]}),

.m_axis_data_tvalid(m_axis_data_tvalid[i]),

.m_axis_data_tdata({sine[i],cosine[i]}),

.m_axis_phase_tvalid(m_axis_phase_tvalid[i]),

.m_axis_phase_tdata(m_axis_phase_tdata[i])

);

end

endgenerate