了解预设文件

预设文件有助于在特定配置中自定义IP核心。PS7、axi_emc和当linear_flash或DDR3_SDRAM

界面是在Vivado IP集成商的Board选项卡中选择的。预设文件使用XML格式。preset_file是为特定的Board文件定义的,可以是用于将预设应用于多个IP。

<ip_presets schema="1.0">

<ip_preset preset_proc_name="emc_preset">

<ip vendor="xilinx.com" library="ip" name="axi_emc" version="3.0">

<user_parameters>

<user_parameter name="CONFIG.C_INCLUDE_DATAWIDTH_MATCHING_0"

value="1"/>

<user_parameter name="CONFIG.C_MAX_MEM_WIDTH" value="16"/>

<user_parameter name="CONFIG.C_MEM0_TYPE" value="2"/>

<user_parameter name="CONFIG.C_MEM0_WIDTH" value="16"/>

<user_parameter name="CONFIG.C_TAVDV_PS_MEM_0" value="130000"/>

<user_parameter name="CONFIG.C_TCEDV_PS_MEM_0" value="130000"/>

<user_parameter name="CONFIG.C_TWPH_PS_MEM_0" value="12000"/>

<user_parameter name="CONFIG.C_TWP_PS_MEM_0" value="70000"/>

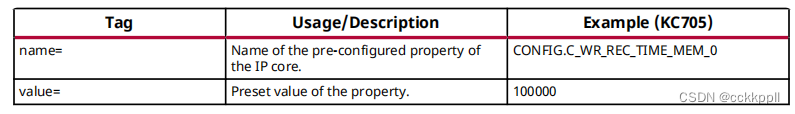

<user_parameter name="CONFIG.C_WR_REC_TIME_MEM_0" value="100000"/>

</user_parameters>

</ip>

</ip_preset>

<ip_preset preset_proc_name="ddr3_sdram_preset">

<ip vendor="xilinx.com" library="ip" name="mig_7series">

<user_parameters>

<user_parameter name="CONFIG.XML_INPUT_FILE" value="mig.prj"

value_type="file"/>

</user_parameters>

</ip>

</ip_preset>

</ip_presets>

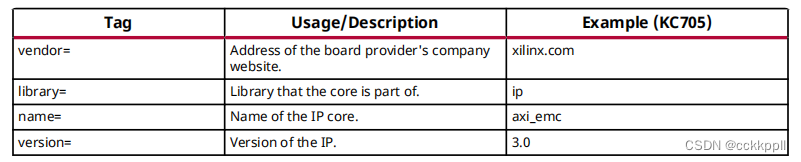

IP设置(_P)

<ip_presets>是preset_file的根,并定义一个或多个ip的预设核心。<ip_preset>中可以嵌套一个或多个<ip_prreset>标记。

<ip_presets schema="1.0">

IP设置(_P)

<ip_preset>部分定义了要应用于特定ip核心的预设配置。

<ip_preset preset_proc_name="emc_preset">

IP

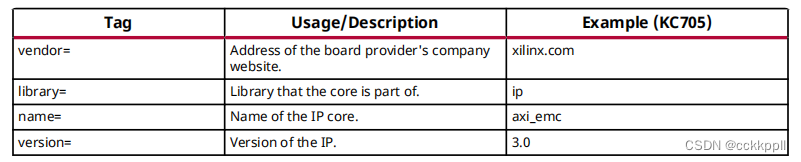

在<ip_preset>中,<ip>部分定义了预设值将应用的特定ip到

<ip vendor="xilinx.com" library="ip" name="axi_emc" version="3.0">

用户参数

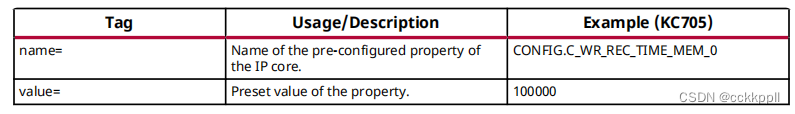

在<ip>部分中,<user_parameters>和<user_paarameters>标记定义了要应用于指定IP核心的配置预设。

<user_parameters>

<user_parameter name="CONFIG.C_INCLUDE_DATAWIDTH_MATCHING_0" value="1"/>

<user_parameter name="CONFIG.C_MAX_MEM_WIDTH" value="16"/>

<user_parameter name="CONFIG.C_MEM0_TYPE" value="2"/>

</user_parameter>

附加文件和特殊注意事项

内存IP 7系列支持

AMD 7系列设备中的内存IP需要特殊处理。电路板设计者应测试在将PRJ文件添加到板支持区域之前,板上的内存IP配置。

PS7预设

对于PS7 IP核心,指定预设配置与中任何其他支持的IP相同目录<user_parameters>必须命名各种预配置的属性及其值在preset_file中。

<ip_preset preset_proc_name="ps7_preset">

<ip vendor="xilinx.com" library="ip" name="processing_system7"

version="*">

<user_parameters>

<user_parameter name="CONFIG.preset" value="ZC702"/>

<user_parameter name="CONFIG.PCW_CAN0_PERIPHERAL_ENABLE" value="0"/>

</user_parameters>

</ip>

</ip_preset>

具有三态端口的IP总线接口

IP总线接口暴露三态端口的三个信号(I、O和T)。基于IP配置中,一个或全部三个信号通过三态缓冲器暴露为单个外部端口。在接口逻辑到物理端口映射<port_map>中,仅截取暴露的信号需要为GPIO定义,而对于IO,所有三个信号都需要映射到物理港口城市

实例

<interface mode="master" name="dip_switches_4bits"

type="xilinx.com:interface:gpio_rtl:1.0">

<port_maps>

<port_map logical_port="TRI_I" physical_port="dip_switches_tri_i"/>

</port_maps>

</interface>

<interface mode="master" name="iic_main"

type="xilinx.com:interface:iic_rtl:1.0">

<port_maps>

<port_map logical_port="SDA_I" physical_port="iic_main_sda_i"/>

<port_map logical_port="SDA_O" physical_port="iic_main_sda_o"/>

<port_map logical_port="SDA_T" physical_port="iic_main_sda_t"/>

<port_map logical_port="SCL_I" physical_port="iic_main_scl_i"/>

<port_map logical_port="SCL_O" physical_port="iic_main_scl_o"/>

<port_map logical_port="SCL_T" physical_port="iic_main_scl_t"/>

</port_maps>

</interface>

以太网时钟处理

为了区分以太网时钟和常规时钟,接口参数“TYPE”在中定义架构。此参数在搜索适当的IP时提供额外的筛选板接口。TYPE参数的值在板接口中应相同,并且IP接口。例如,KC705板中的sgmii_mgt_clk接口的TYPE参数为GT_ CLK定义的值。类似地,IP component.xml文件具有接口参数TYPE=ETH_MGT_CLK。请参阅<vivado_install_dir>/data/ip/xilinx/gig_ethernet_pcs_pma_v15_0/component.xml实例

GT位置限制

为了生成GT位置约束,以太网相关接口在中具有GT_LOC参数板接口。例如,KC705板的sgmii接口具有GT_LOC=GTXE2_CHANNEL_X0Y9。此处,以太网IP假设如果中不存在此参数板接口,然后它在LVDS模式下运行,因此IP自定义

IP板意识

对于AMD目标参考平台或评估板,IP了解FPGA引脚在目标板上使用的。这就是所谓的董事会意识。基于该信息IP集成板/连接自动化功能可以帮助您绑定IP接口/端口连接到板上的外部端口。IP集成商然后创建适当的物理约束有问题的I/O端口所需的其他I/O约束。

当前可识别板的IP列表:

axi_emc_v3_0

axi_ethernet_buffer_v2_0

axi_ethernet_v7_2

axi_ethernetlite_v3_0

axi_gpio_v2_0

axi_iic_v2_1

axi_noc_v1_0

axi_pcie3_v3_0

axi_quad_spi_v3_2

axi_uart16550_v2_0

axi_uartlite_v2_0

clk_gen_sim_v1_0

clk_wiz_v5_4

clk_wiz_v6_0

clk_wizard_v1_0

cmac_usplus_v3_1

cmac_v2_6

ddr3_v1_4

ddr4_pl_v1_0

ddr4_v2_2

ethernet_1_10_25g_v2_7

gig_ethernet_pcs_pma_v16_2

i2s_receiver_v1_0

i2s_transmitter_v1_0

interlaken_v2_4

iomodule_v3_1

l_ethernet_v3_2

microblaze_mcs_v2_3

microblaze_mcs_v3_0

mig_7series_v4_2

mipi_csi2_rx_subsystem_v5_1

mipi_dphy_v4_3

mipi_dsi_tx_subsystem_v2_2

mrmac_v1_6

pcie4_uscale_plus_v1_3

pcie4c_uscale_plus_v1_0

pcie_3port_switch_v1_0

pcie_dma_versal_v2_0

pcie_versal_v1_0

proc_sys_reset_v5_0

qdma_v4_0

system_management_wiz_v1_3

tmr_comparator_v1_0

tmr_sem_v1_0

tmr_voter_v1_0

tri_mode_ethernet_mac_v9_0

tsn_temac_v1_0

usxgmii_v1_2

vcu_ddr4_controller_v1_1

versal_cips_v3_2

xdma_v4_1

xxv_ethernet_v4_0

![[SwiftUI]修改状态栏文字颜色](https://img-blog.csdnimg.cn/direct/2174f59c72a843a7a721f589f1975a0b.jpeg)