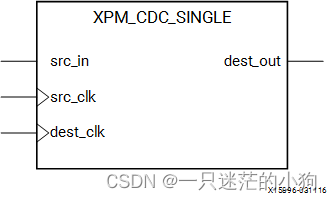

Parameterized Macro: Single-bit Synchronizer(参数化宏:单比特同步器)

- MACRO_GROUP: XPM

- MACRO_SUBGROUP: XPM_CDC

- Families: UltraScale, UltraScale+

1、 Introduction(介绍)

此宏将一个一位信号从源时钟域同步到目标时钟域。为了正确操作,输入数据必须由目标时钟采样两次或两次以上。您可以定义同步器中使用的寄存器级数。可选的输入寄存器可以用于在源时钟域中的输入被同步之前将其寄存。还可以启用仿真特性来生成消息,以报告宏的任何潜在滥用。

2、Port Descriptions(端口描述)

| 端口 | 方向 | 宽度 | 时钟域 | 敏感类型 | 未使用时处理方式 | 功能 |

| dst_clk | 输入 | 1 | NA | 边沿敏感 | 激活 | 目的时钟域的时钟信号 |

| dest_out | 输出 | 1 | dst_clk | NA | 激活 | 要被同步到目的时钟的信号,为寄存器类型 |

| src_clk | 1 | NA | 边沿敏感 | 0 | 当SRC_INPUT_REG = 1.时,为src_in的输入时钟,SRC_INPUT_REG = 0时未使用 | |

| src_in | 1 | src_clk | NA | 激活 | 要被同步到dest_clk时钟域的输入信号 |

3、Design Entry Method(设计输入方法)

| 实例化 | 是 |

| 引用 | 否 |

| IP和IP Intergator Catalog | 否 |

4、Available Attributes(可用属性)

| 属性 | 类型 | 允许值 | 默认值 | 描述 |

| DEST_SYNC_FF | 十进制 | 2—10 | 4 | 用于同步目标时钟域中的信号的寄存器级数。 |

| INIT_SYNC_FF | 十进制 | 0,1 | 0 | 0-禁用同步寄存器上的行为模拟初始化值。 1-在同步寄存器上启用行为模拟初始化值。 |

| SIM_ASSERT_CHK | 十进制 | 0,1 | 0 | 0-禁用模拟消息报告。与潜在滥用相关的信息将不会被报告。 1-启用模拟消息报告。将报告与潜在滥用有关的信息。 |

| SRC_INPUT_REG | 十进制 | 1,0 | 1 | 0-不注册输入(src_in) 1-使用src_clk注册输入(src_in)一次 |

5、VHDL Instantiation Template(VHDL实例化模板)

除非它们已经存在,否则复制以下两个语句并将它们粘贴在实体声明之前。

Library xpm;

use xpm.vcomponents.all;-- xpm_cdc_single: Single-bit Synchronizer

-- Xilinx Parameterized Macro, version 2023.1

xpm_cdc_single_inst : xpm_cdc_single

generic map (

DEST_SYNC_FF => 4, -- DECIMAL; range: 2-10

INIT_SYNC_FF => 0, -- DECIMAL; 0=disable simulation init values, 1=enable simulation init values

SIM_ASSERT_CHK => 0, -- DECIMAL; 0=disable simulation messages, 1=enable simulation messages

SRC_INPUT_REG => 1 -- DECIMAL; 0=do not register input, 1=register input

)

port map (

dest_out => dest_out, -- 1-bit output: src_in synchronized to the destination clock domain. This output

-- is registered.

dest_clk => dest_clk, -- 1-bit input: Clock signal for the destination clock domain.

src_clk => src_clk, -- 1-bit input: optional; required when SRC_INPUT_REG = 1

src_in => src_in -- 1-bit input: Input signal to be synchronized to dest_clk domain.

);

-- End of xpm_cdc_single_inst instantiation6、Verilog Instantiation Template

// xpm_cdc_single: Single-bit Synchronizer

// Xilinx Parameterized Macro, version 2023.1

xpm_cdc_single #(

.DEST_SYNC_FF(4), // DECIMAL; range: 2-10

.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values

.SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages

.SRC_INPUT_REG(1) // DECIMAL; 0=do not register input, 1=register input

)

xpm_cdc_single_inst (

.dest_out(dest_out), // 1-bit output: src_in synchronized to the destination clock domain. This output is

// registered.

.dest_clk(dest_clk), // 1-bit input: Clock signal for the destination clock domain.

.src_clk(src_clk), // 1-bit input: optional; required when SRC_INPUT_REG = 1

.src_in(src_in) // 1-bit input: Input signal to be synchronized to dest_clk domain.

);

// End of xpm_cdc_single_inst instantiation