一 目标

针对资源受限,SWaP敏感的边缘计算应用场景,探索稳健而高效的计算架构,算法和应用。 并完成超轻量级神经网络加速器设计和验证。

1、实时性能:30~50FPS

2、超低功耗:mW级别

3、资源受限:包括计算资源/存储资源/通信带宽等

4、成本低廉:

二 设计分析

。。。

三 验证

网络模型:优化设计的YOLOV3

FPGA硬件平台:ZYNQ7020

性能:35FPS(150MHz)

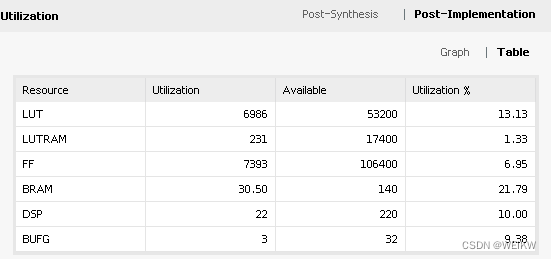

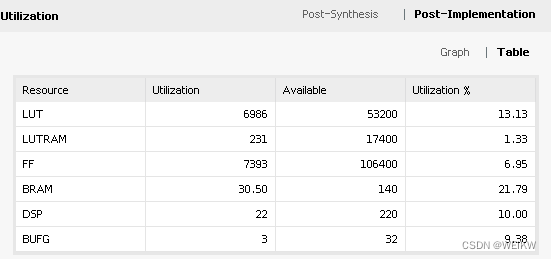

资源消耗7K LUT

四 参考文献

[1] TinyNPU

[2] DAC-SDC

一 目标

针对资源受限,SWaP敏感的边缘计算应用场景,探索稳健而高效的计算架构,算法和应用。 并完成超轻量级神经网络加速器设计和验证。

1、实时性能:30~50FPS

2、超低功耗:mW级别

3、资源受限:包括计算资源/存储资源/通信带宽等

4、成本低廉:

二 设计分析

。。。

三 验证

网络模型:优化设计的YOLOV3

FPGA硬件平台:ZYNQ7020

性能:35FPS(150MHz)

资源消耗7K LUT

四 参考文献

[1] TinyNPU

[2] DAC-SDC

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/1078566.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!